# **Design Considerations for Logic Products**

Volume 3

December 2000

Logic Products

SDYA019

# **Design Considerations** for Logic Products

Ÿ

December 2000

# **Design Considerations for Logic Products**

December 2000

Logic Products

SDYA019

# Design Considerations for Logic Products

Ų

December 2000

Application Book Volume 3

| General Design Considerations  | 1 |

|--------------------------------|---|

| Device-Specific Design Aspects | 2 |

| Packaging                      | 3 |

| Index                          | 4 |

| Appendix A                     | Α |

| General Design Considerations  | 1 |  |

|--------------------------------|---|--|

| Device-Specific Design Aspects | 2 |  |

| Packaging                      | 3 |  |

| Index                          | 4 |  |

| Appendix A                     | Α |  |

|                                                                                         | Page  |

|-----------------------------------------------------------------------------------------|-------|

| Input and Output Characteristics of Digital Integrated Circuits at 5-V Supply Voltage   | 1–3   |

| Input and Output Characteristics of Digital Integrated Circuits at 3.3-V Supply Voltage | 1–57  |

| Input and Output Characteristics of Digital Integrated Circuits at 2.5-V Supply Voltage | 1-87  |

| Benefits and Issues on Migration of 5-V and 3.3-V Logic to Lower-Voltage Supplies       | 1–113 |

| Voltage Translation (5 V, 3.3 V, 2.5 V, 1.8 V), Switching Standards, and Bus Contention | 1–141 |

| PCB Design Guidelines For Reduced EMI                                                   | 1–155 |

| Electromagnetic Emission From Logic Circuits                                            | 1–181 |

| Latch-Up, ESD, and Other Phenomena                                                      | 1-225 |

| General Design Considerations  | 1 |

|--------------------------------|---|

| Device-Specific Design Aspects | 2 |

| Packaging                      | 3 |

| Index                          | 4 |

| Appendix A                     | Α |

|                                                                       | Page |

|-----------------------------------------------------------------------|------|

| Flexible Voltage-Level Translation With CBT Family Devices            | 2–3  |

| Texas Instruments Solution for Undershoot Protection for Bus Switches | 2–9  |

| Designing With the SN74AHC123A and SN74AHCT123A                       | 2–19 |

| Advanced Low-Voltage Technology                                       | 2–39 |

| General Design Considerations  | 1 |

|--------------------------------|---|

| Device-Specific Design Aspects | 2 |

| Packaging                      | 3 |

| Index                          | 4 |

| Appendix A                     | Α |

|                                                                              | Page |

|------------------------------------------------------------------------------|------|

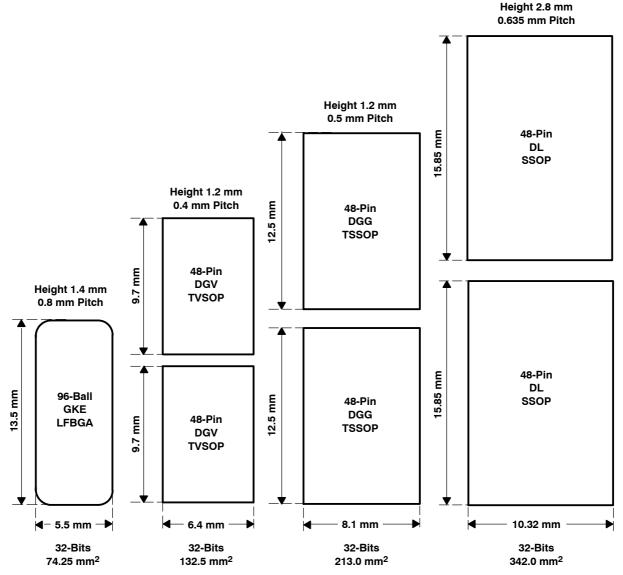

| Comparison of Electrical and Thermal Parameters of                           |      |

| Widebus™ SMD SSOP, TSSOP, TVSOP, and LFBGA Packages                          | 3–3  |

| Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs | 3–47 |

| Standard Linear & Logic Semiconductor Marking Guidelines                     | 3–57 |

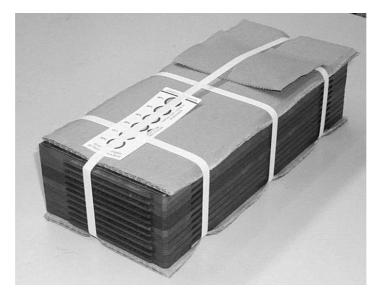

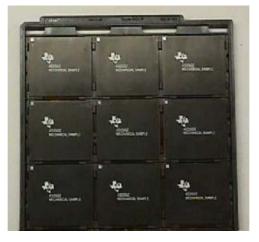

| Semiconductor Packing Methodology                                            | 3–69 |

| General Design Considerations  | 1 |

|--------------------------------|---|

| Device-Specific Design Aspects | 2 |

| Packaging                      | 3 |

| Index                          | 4 |

| Appendix A                     | Α |

4 Index

| General Design Considerations  | 1 |

|--------------------------------|---|

| Device-Specific Design Aspects | 2 |

| Packaging                      | 3 |

| Index                          | 4 |

| Appendix A                     | Α |

# Design Considerations for Logic Products Application Book

Volume 3

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

### INTRODUCTION

This collection of application reports and articles provides the design engineer with a valuable technical reference for Texas Instruments' products. It contains application reports written or revised between August 1999 and August 2000. This book is divided into three sections, each focusing on different aspects of design decisions. An index is included to make it easy to find the information.

Section 1, *General Design Considerations*, includes discussions of using digital integrated circuits with 5-, 3.3-, and 2.5-V power supplies, migration to lower voltages, voltage translation, and other considerations when designing with TI logic devices.

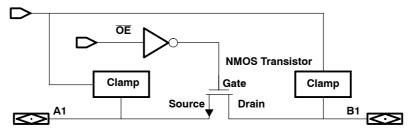

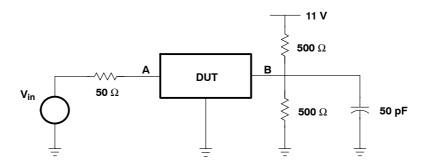

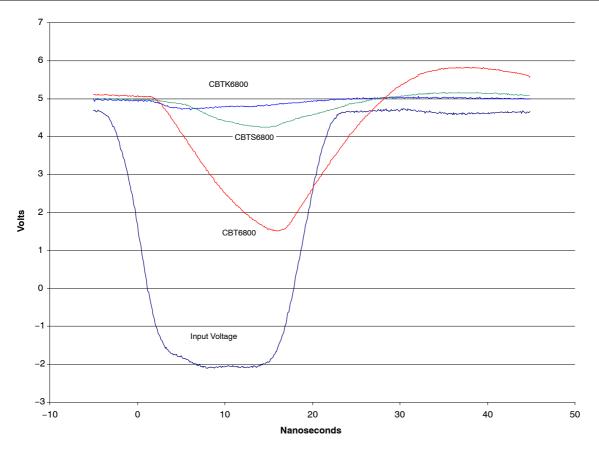

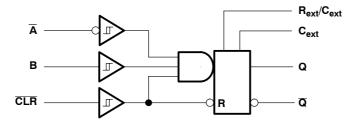

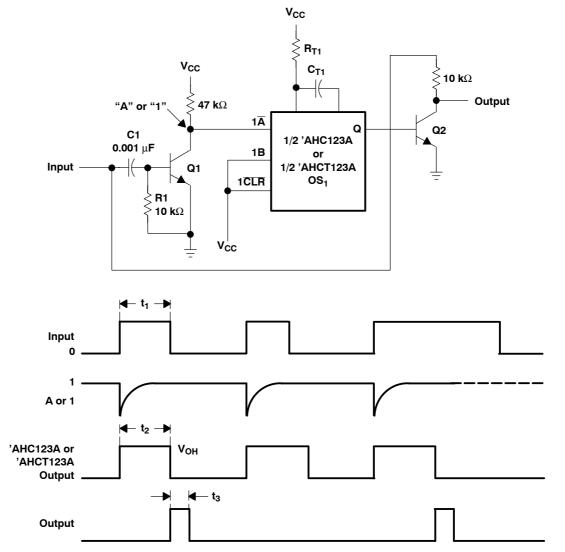

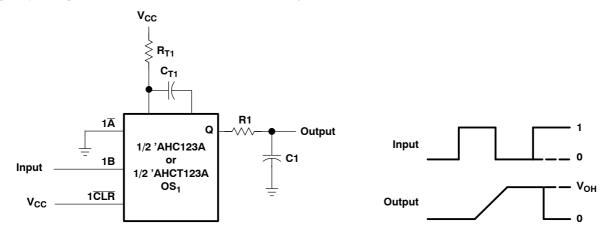

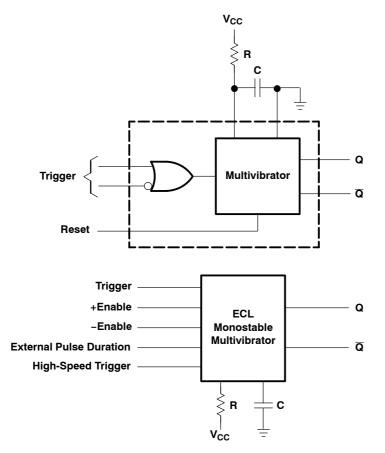

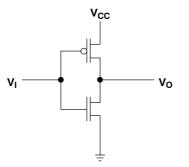

Section 2, *Device-Specific Design Aspects*, focuses on features specific to a device or family of devices, including CBT in flexible voltage-level translation, the new CBTK active-clamp feature, AHC/AHCT123A monostable multivibrators, and the Advanced Low-Voltage Technology (ALVT) family.

Section 3, *Packaging*, gives an overview of electrical and thermal parameters, logic-device marking guidelines, and packing methodology to help you select the best advanced-logic-device package for your design.

For more information on these and other TI products, please contact your local TI representative, authorized distributor, the TI technical support hotline at 972-644-5580, or visit the TI logic home page at http://www.ti.com/sc/logic. Application reports published in previous volumes of the *Design Considerations for Logic Products* Application Book (see Appendix A) also are available through links on the TI logic home page.

| Section 1 – General Design Considerations                                                 | 1–1   |

|-------------------------------------------------------------------------------------------|-------|

| Input and Output Characteristics of Digital Integrated Circuits at 5-V Supply Voltage     | 1–3   |

| Input and Output Characteristics of Digital Integrated Circuits at 3.3-V Supply Voltage   | 1–57  |

| Input and Output Characteristics of Digital Integrated Circuits at 2.5-V Supply Voltage   | 1–87  |

| Benefits and Issues on Migration of 5-V and 3.3-V Logic to Lower-Voltage Supplies         | 1–113 |

| Voltage Translation (5 V, 3.3 V, 2.5 V, 1.8 V), Switching Standards, and Bus Contention . | 1–141 |

| PCB Design Guidelines For Reduced EMI                                                     | 1–155 |

| Electromagnetic Emission From Logic Circuits                                              | 1–181 |

| Latch-Up, ESD, and Other Phenomena                                                        | 1–225 |

| Section 2 – Device-Specific Design Aspects                                                | 2–1   |

| Flexible Voltage-Level Translation With CBT Family Devices                                | 2–3   |

| Texas Instruments Solution for Undershoot Protection for Bus Switches                     | 2–9   |

| Designing With the SN74AHC123A and SN74AHCT123A                                           | 2–19  |

| Advanced Low-Voltage Technology                                                           | 2–39  |

| Section 3 – Packaging                                                                     | 3–1   |

| Comparison of Electrical and Thermal Parameters of                                        |       |

| Widebus™ SMD SSOP, TSSOP, TVSOP, and LFBGA Packages                                       |       |

| Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs              |       |

| Standard Linear & Logic Semiconductor Marking Guidelines                                  |       |

| Semiconductor Packing Methodology                                                         | 3–69  |

| Section 4 – Index                                                                         | 4–1   |

| Appendix A                                                                                | A-1   |

| Design Considerations for Logic Products Application Book, Volume 1, Contents             | A–3   |

# Input and Output Characteristics of Digital Integrated Circuits at 5-V Supply Voltage

SZZA008 September 1999

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

# Title

| A | bstract                                                                                                                                      | 1-9  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1 | Introduction                                                                                                                                 | 1-9  |

| 2 | Input Characteristics                                                                                                                        | 1-11 |

| 3 | Output Characteristics                                                                                                                       | 1-18 |

| 4 | Bergeron Method Applied to the SN74AHC240         4.1 Voltage Value at the Output of the Driver         4.2 Voltage Value at End of the Line | 1-35 |

| 5 | Output Waveforms                                                                                                                             | 1-38 |

| 6 | Abbreviations and Glossary                                                                                                                   | 1-53 |

| 7 | References         7.1 Documents Published by TI         7.2 Internet Information Sources                                                    | 1–55 |

| 8 | Acknowledgment                                                                                                                               | 1–55 |

### **List of Illustrations**

| Figure | Title                                         | Page |

|--------|-----------------------------------------------|------|

| 1      | Input Characteristic of the SN74xxx Series    | 1–11 |

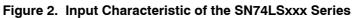

| 2      | Input Characteristic of the SN74LSxxx Series  | 1-12 |

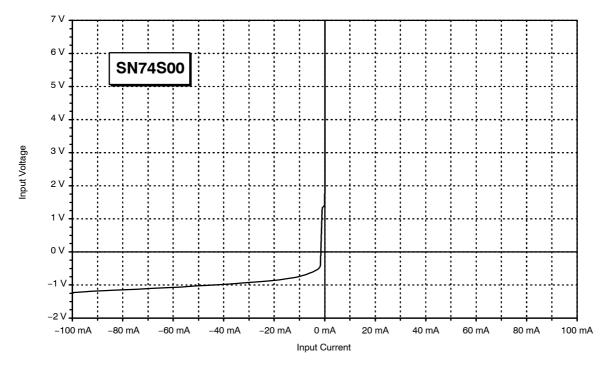

| 3      | Input Characteristic of the SN74Sxxx Series   | 1–12 |

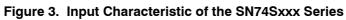

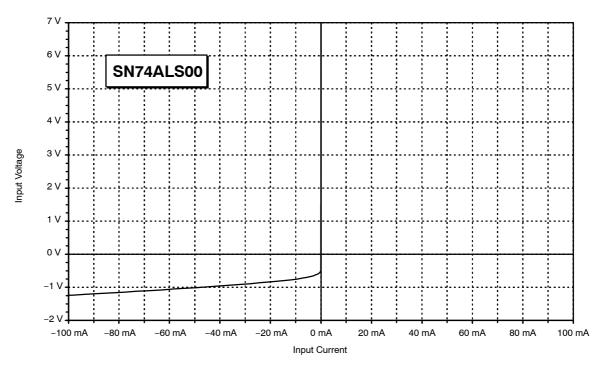

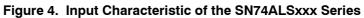

| 4      | Input Characteristic of the SN74ALSxxx Series | 1–13 |

| 5      | Input Characteristic of the SN74ASxxx Series  | 1–13 |

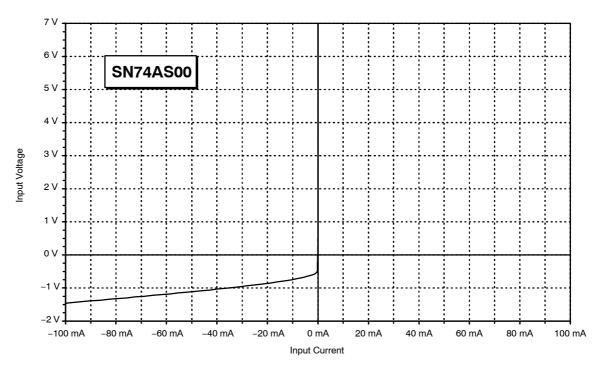

| 6      | Input Characteristic of the SN74Fxxx Series   | 1–14 |

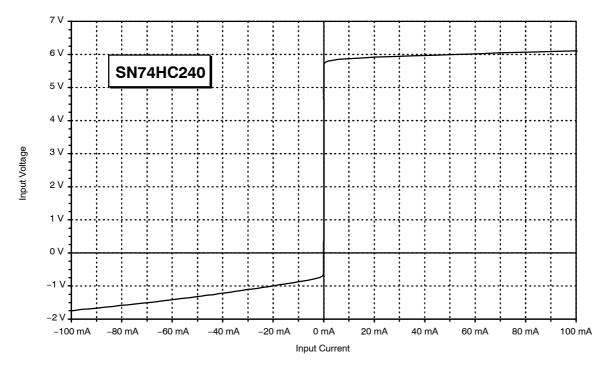

| 7      | Input Characteristic of the SN74HCxxx Series  | 1–14 |

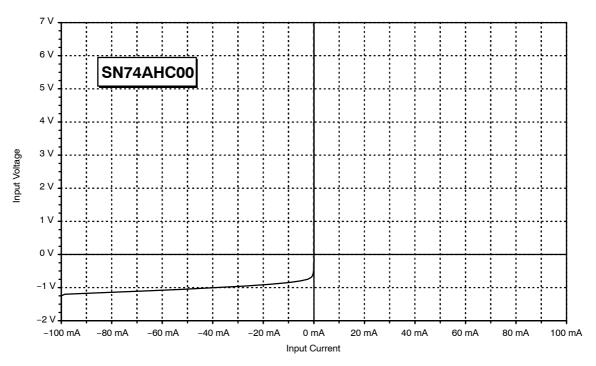

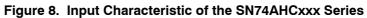

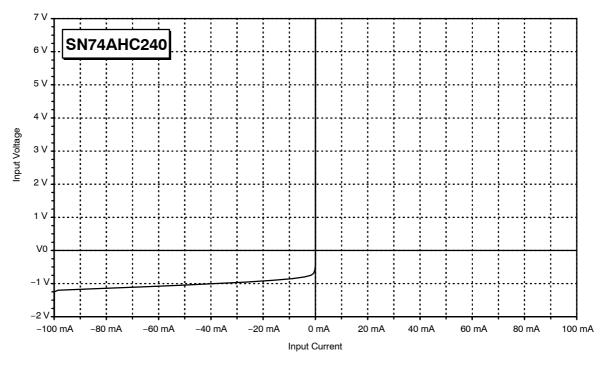

| 8      | Input Characteristic of the SN74AHCxxx Series | 1–15 |

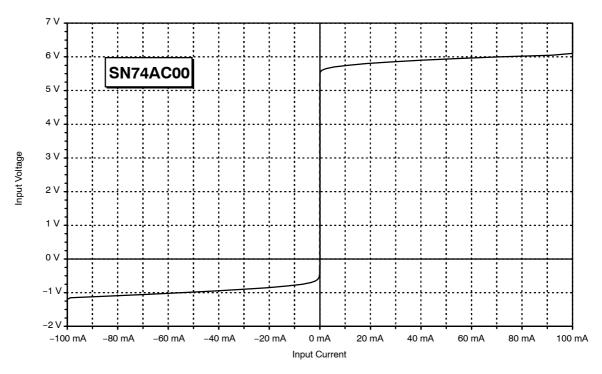

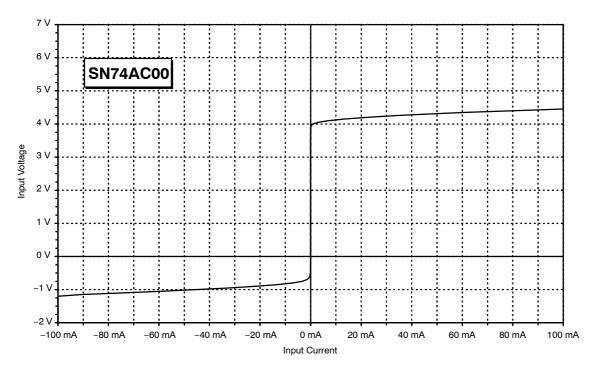

| 9      | Input Characteristic of the SN74ACxxx Series  | 1–15 |

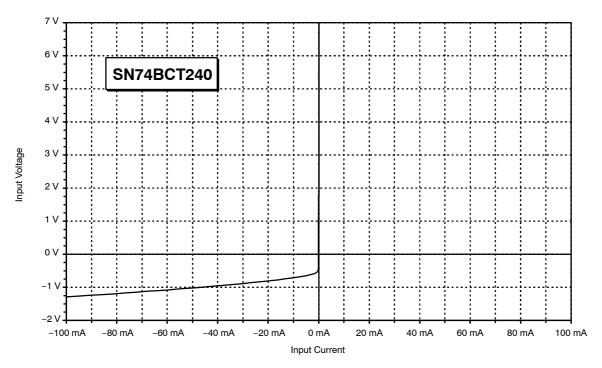

| 10     | Input Characteristic of the SN74BCTxxx Series | 1–16 |

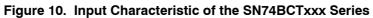

| 11     | Input Characteristic of the SN74ABTxxx Series | 1–16 |

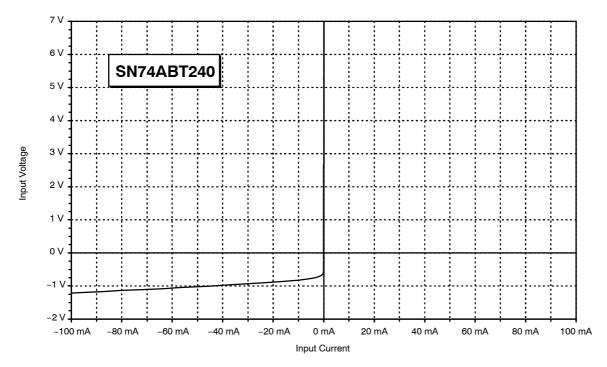

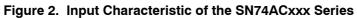

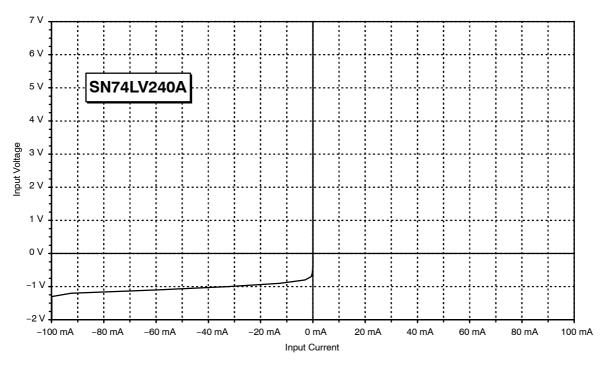

| 12     | Input Characteristic of the SN74LVxxx Series  | 1–17 |

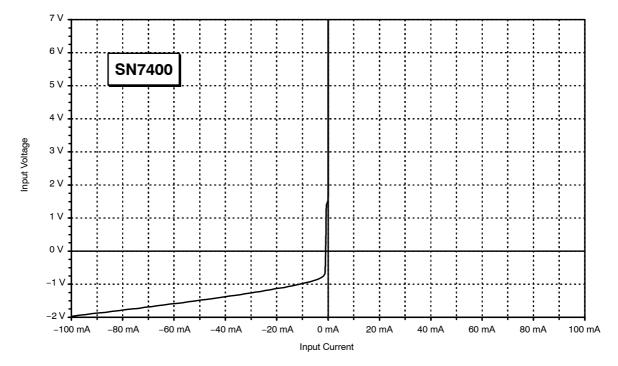

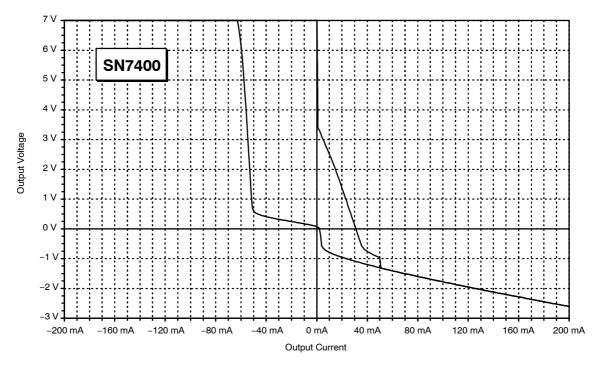

| 13     | Output Characteristic of the SN7400           | 1–18 |

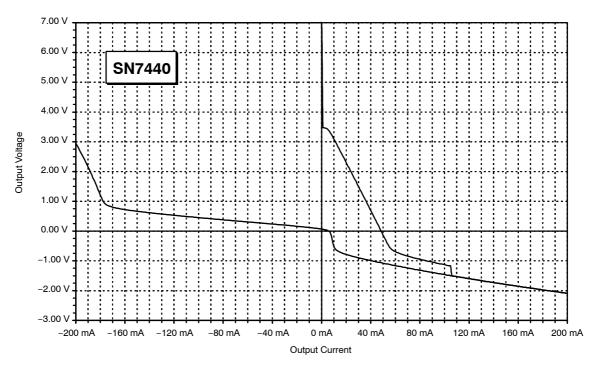

| 14     | Output Characteristic of the SN7440           | 1–19 |

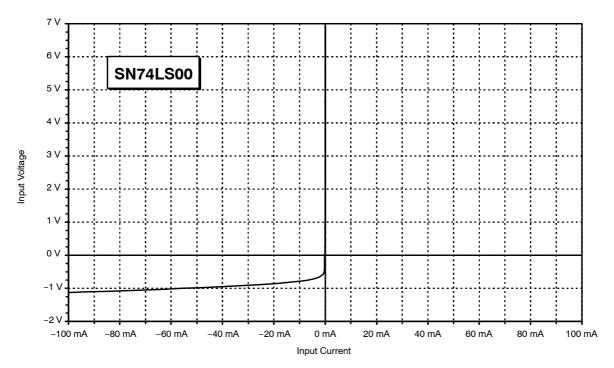

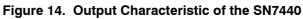

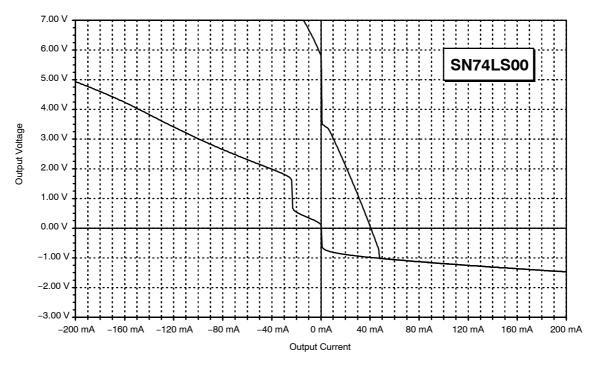

| 15     | Output Characteristic of the SN74LS00         | 1–19 |

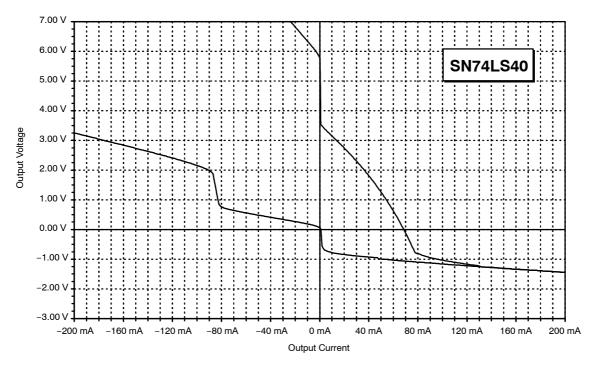

| 16     | Output Characteristic of the SN74LS40         | 1-20 |

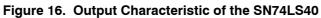

| 17     | Output Characteristic of the SN74LS240        | 1-20 |

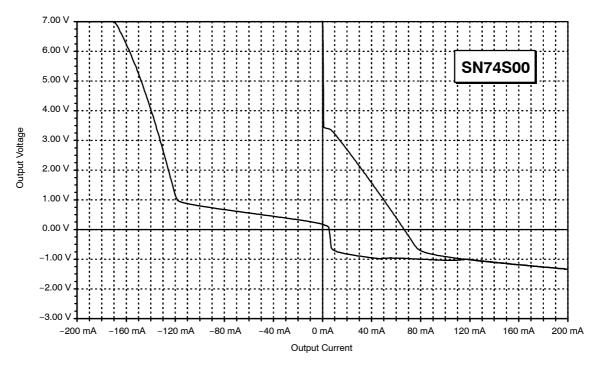

| 18     | Output Characteristic of the SN74S00          | 1–21 |

# List of Illustrations (Continued)

| Figure | Title                                          | Page |

|--------|------------------------------------------------|------|

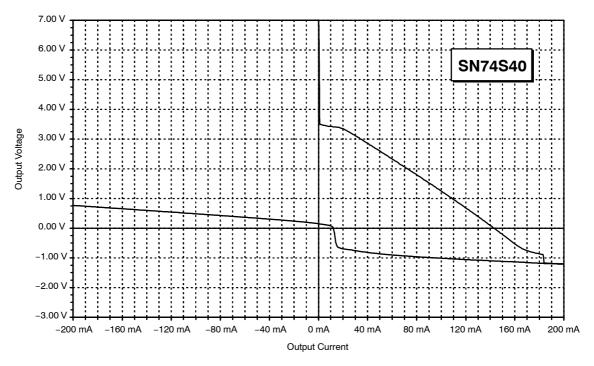

| 19     | Output Characteristic of the SN74S40           | 1–21 |

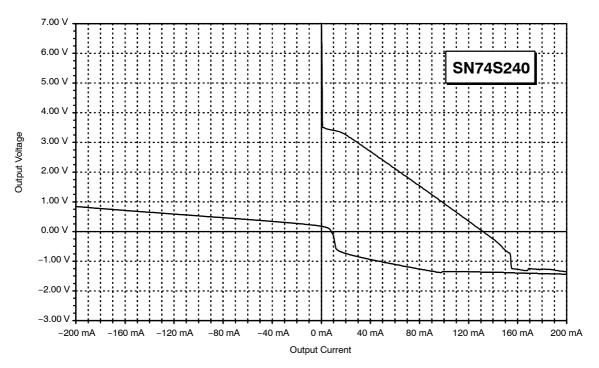

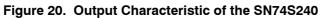

| 20     | Output Characteristic of the SN74S240          | 1-22 |

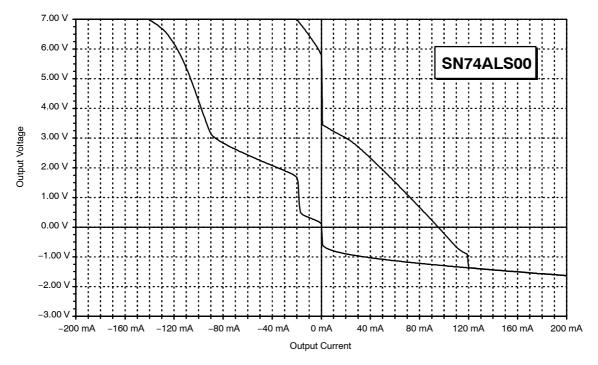

| 21     | Output Characteristic of the SN74ALS00         | 1-22 |

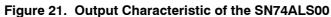

| 22     | Output Characteristic of the SN74ALS40         | 1–23 |

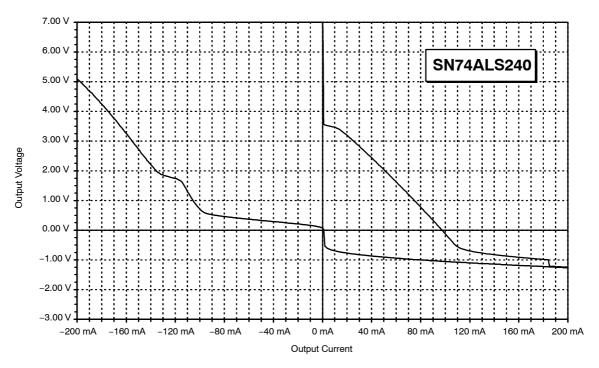

| 23     | Output Characteristic of the SN74ALS240        | 1-23 |

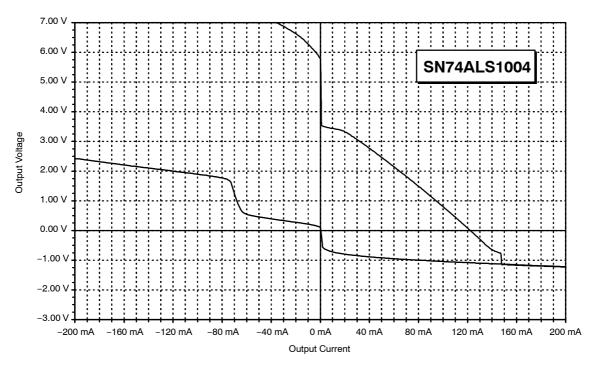

| 24     | Output Characteristic of the SN74ALS1004       | 1–24 |

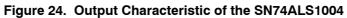

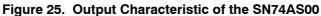

| 25     | Output Characteristic of the SN74AS00          | 1–24 |

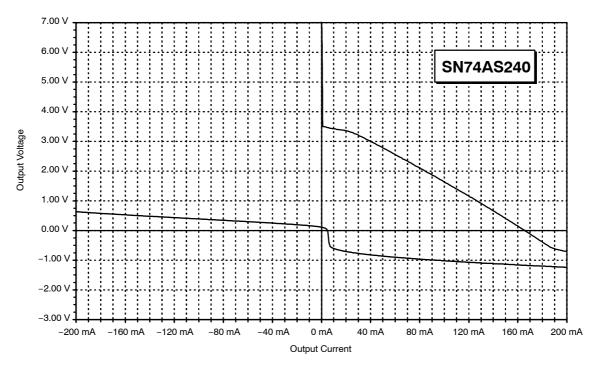

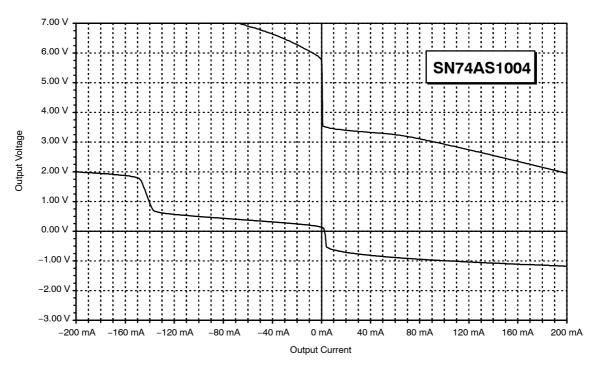

| 26     | Output Characteristic of the SN74AS240         | 1–25 |

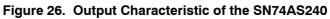

| 27     | Output Characteristic of the SN74AS1004        | 1–25 |

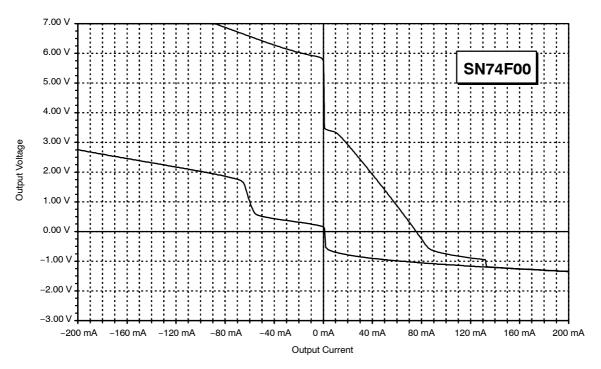

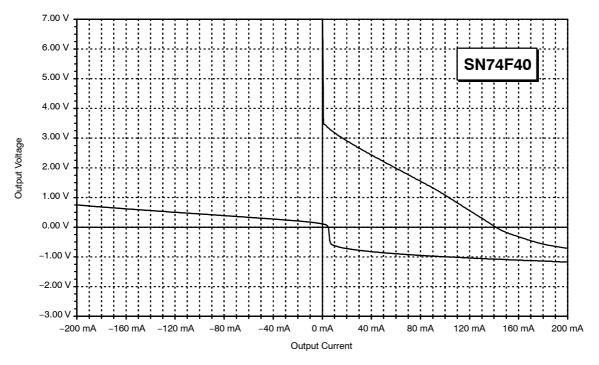

| 28     | Output Characteristic of the SN74F00           | 1-26 |

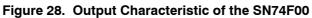

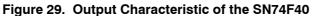

| 29     | Output Characteristic of the SN74F40           | 1–26 |

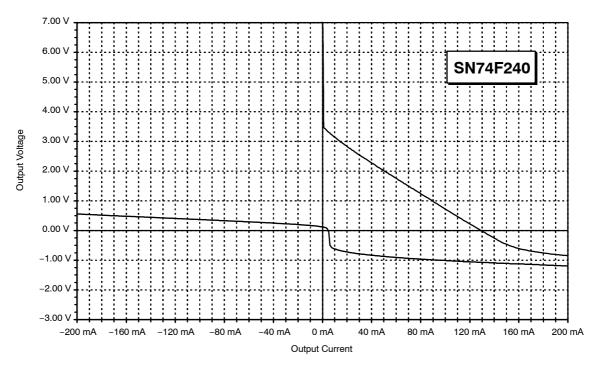

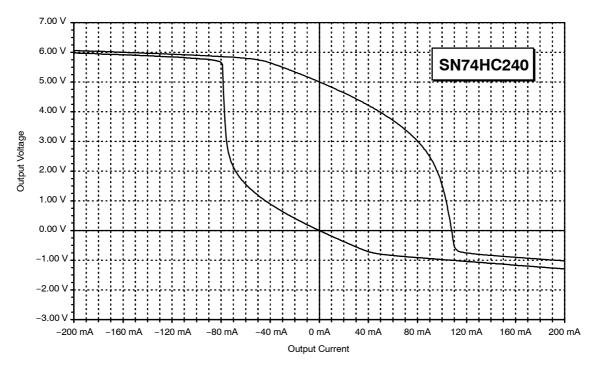

| 30     | Output Characteristic of the SN74F240          | 1–27 |

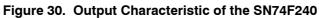

| 31     | Output Characteristic of the SN74HC00          | 1–27 |

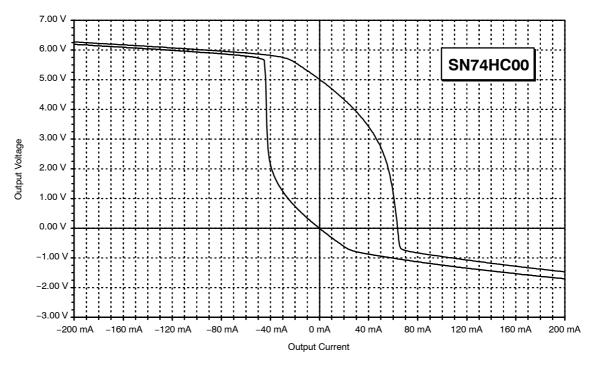

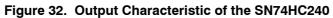

| 32     | Output Characteristic of the SN74HC240         | 1–28 |

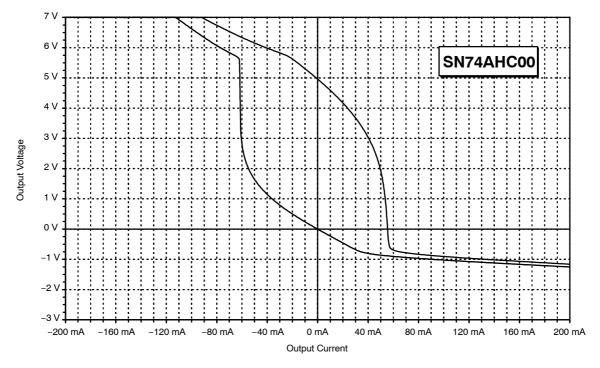

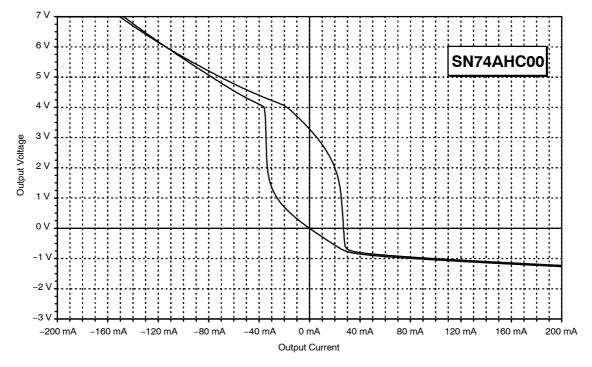

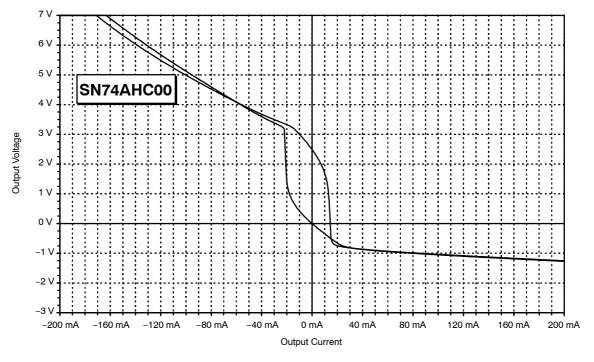

| 33     | Output Characteristic of the SN74AHC00         | 1-28 |

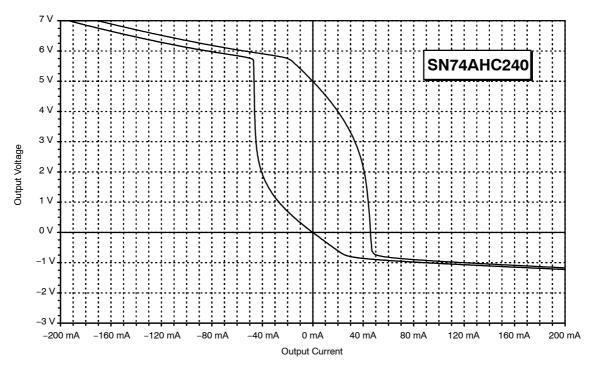

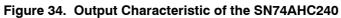

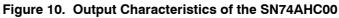

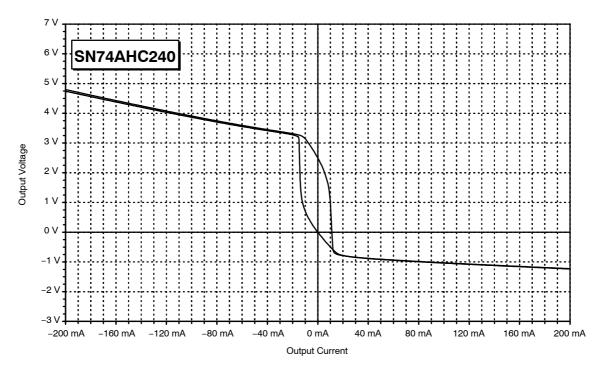

| 34     | Output Characteristic of the SN74AHC240        | 1-29 |

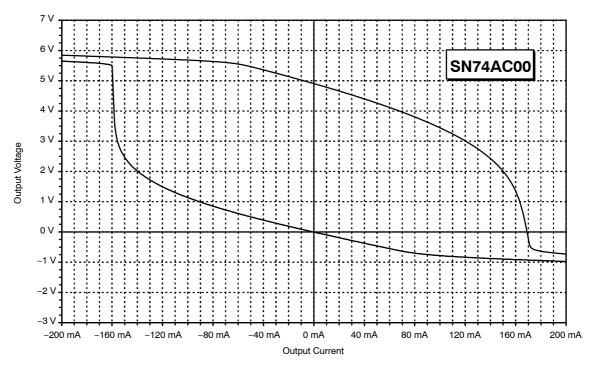

| 35     | Output Characteristic of the SN74AC00          | 1–29 |

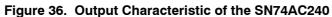

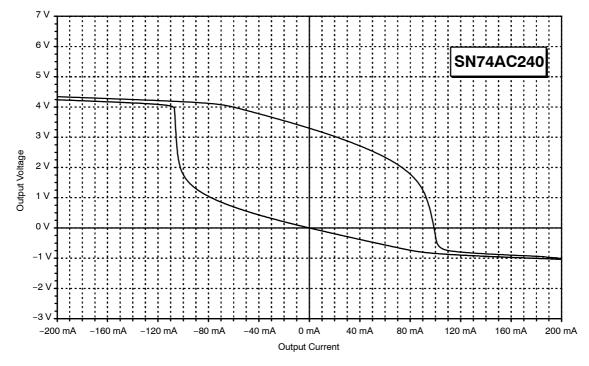

| 36     | Output Characteristic of the SN74AC240         | 1-30 |

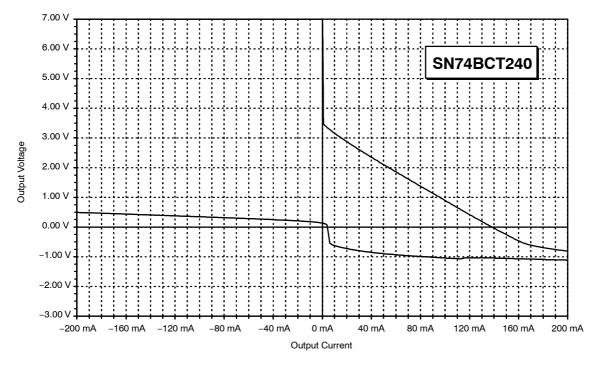

| 37     | Output Characteristic of the SN74BCT240        | 1-30 |

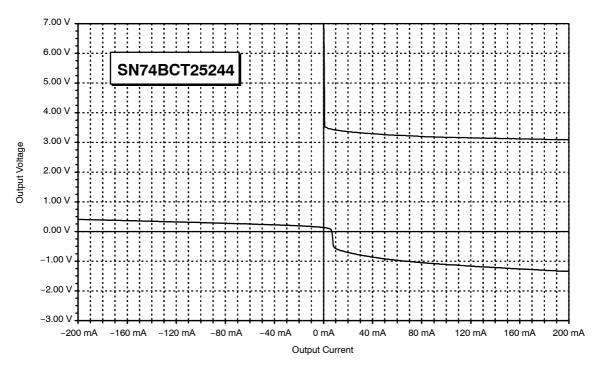

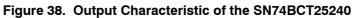

| 38     | Output Characteristic of the SN74BCT25240      | 1–31 |

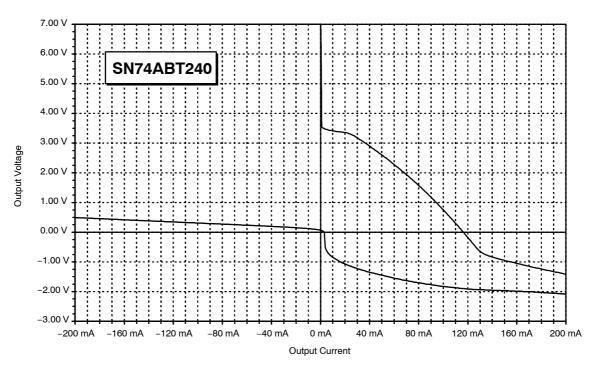

| 39     | Output Characteristic of the SN74ABT240        | 1–31 |

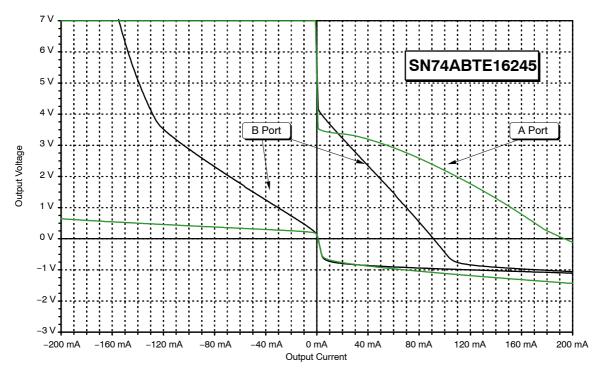

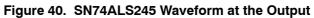

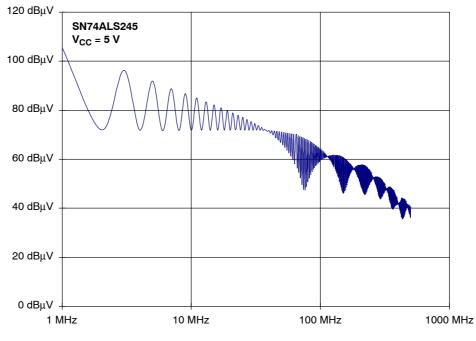

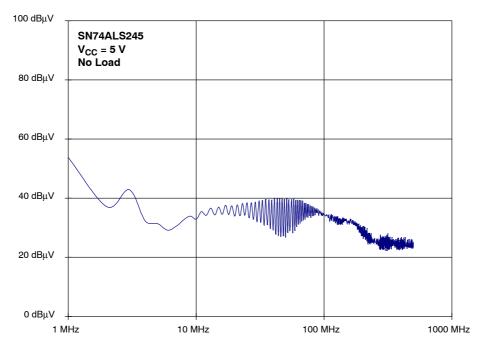

| 40     | Output Characteristic of the SN7ABTE16245      | 1-32 |

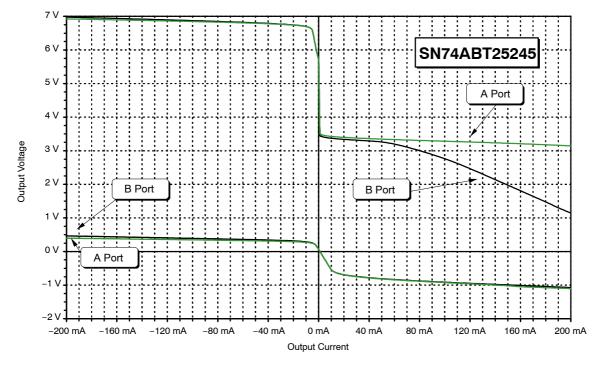

| 41     | Output Characteristic of the SN74ABT25245      | 1-32 |

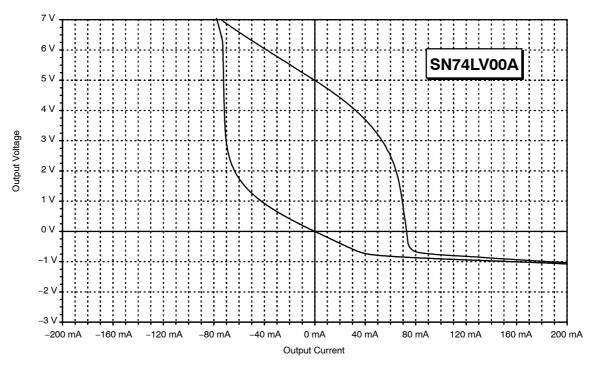

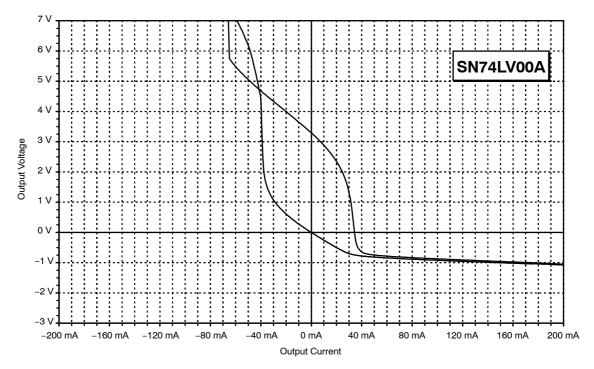

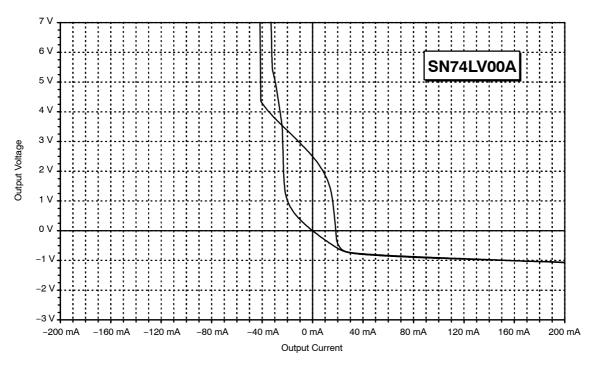

| 42     | Output Characteristic of the SN74LV00A         | 1-33 |

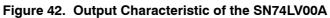

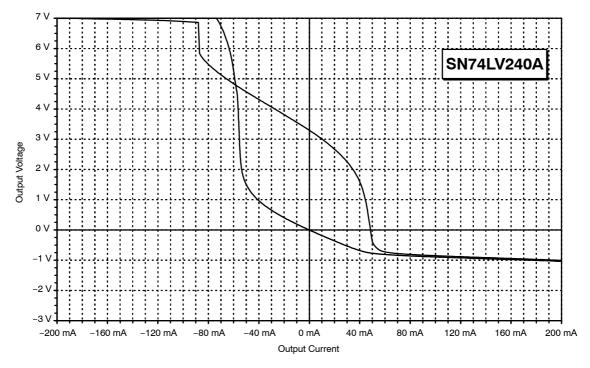

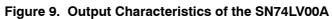

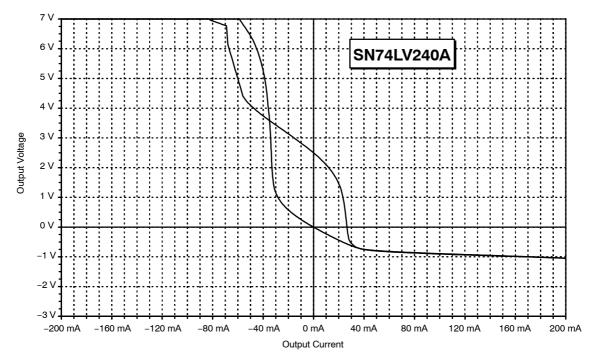

| 43     | Output Characteristic of the SN74LV240A        | 1-33 |

| 44     | Measurement Setup for the Bergeron Method      | 1-34 |

| 45     | Bergeron Diagram for the SN74AHC240            | 1–35 |

| 46     | Diagram of Line Reflections for the SN74AHC240 | 1-36 |

| 47     | Signal Shape of the SN74AHC240                 | 1–37 |

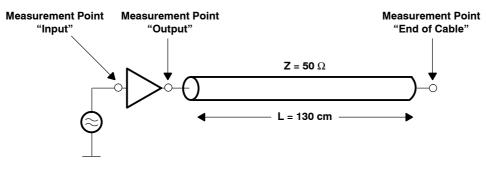

| 48     | Measurement Setup for the Bergeron Method      | 1–38 |

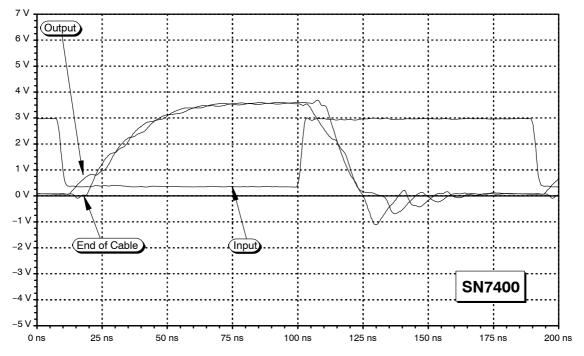

| 49     | Output Waveforms of the SN7400                 | 1–38 |

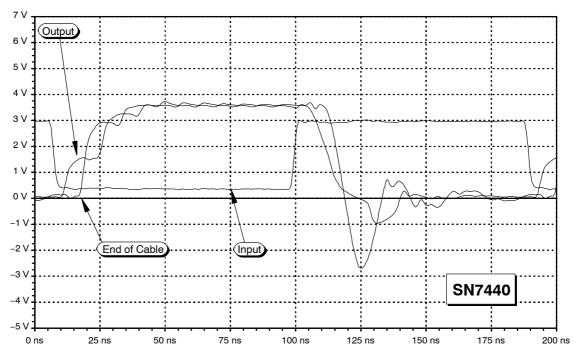

| 50     | Output Waveforms of the SN7440                 | 1-39 |

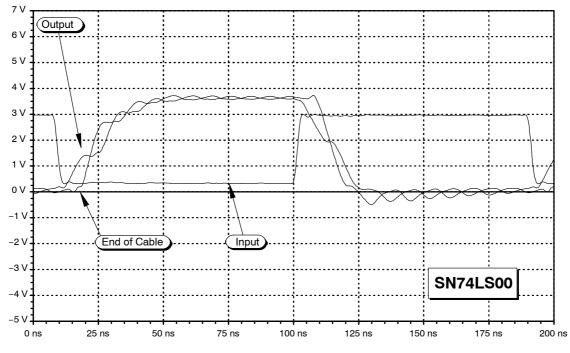

| 51     | Output Waveforms of the SN74LS00               | 1–39 |

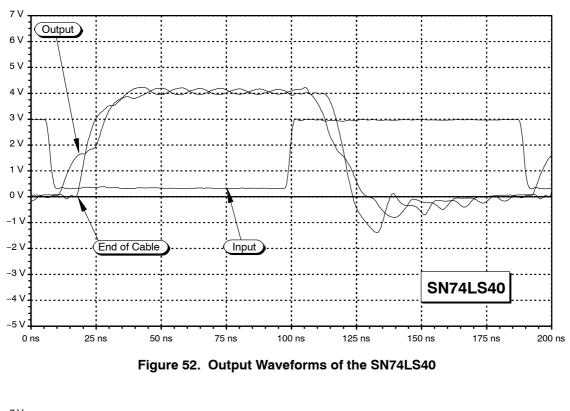

| 52     | Output Waveforms of the SN74LS40               | 1-40 |

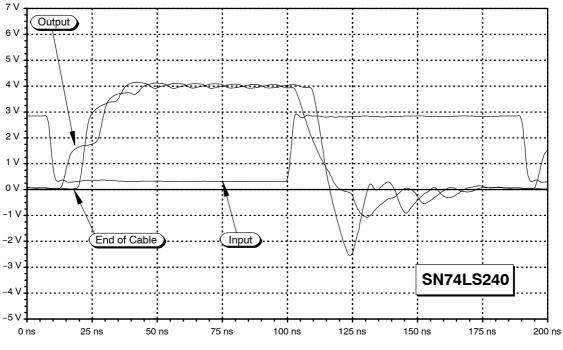

| 53     | Output Waveforms of the SN74LS240              | 1-40 |

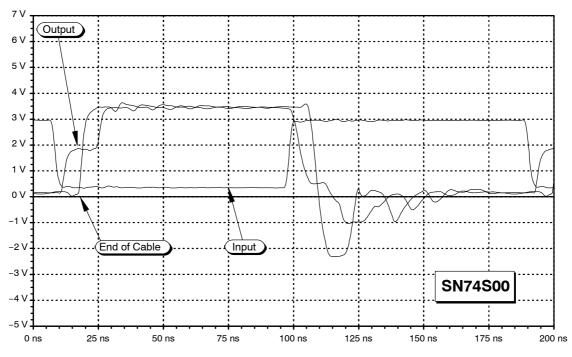

| 54     | Output Waveforms of the SN74S00                | 1–41 |

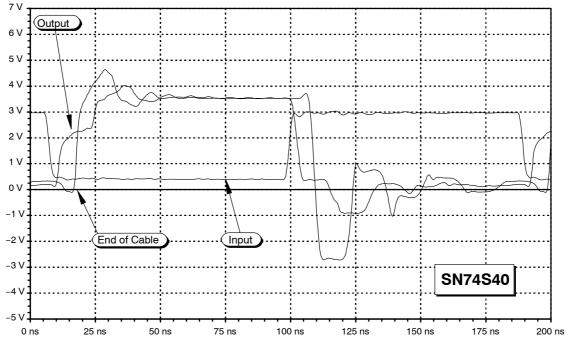

| 55     | Output Waveforms of the SN74S40                | 1–41 |

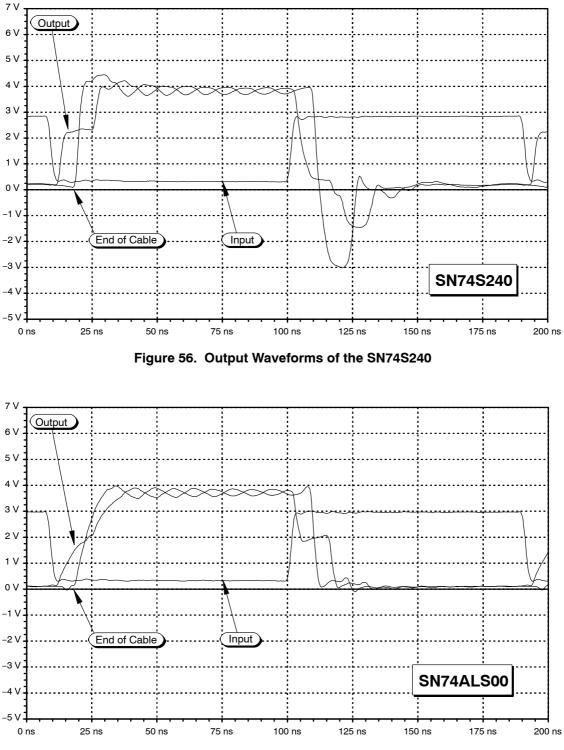

| 56     | Output Waveforms of the SN74S240               | 1-42 |

# List of Illustrations (Continued)

| Figure | Title                                 | Page |

|--------|---------------------------------------|------|

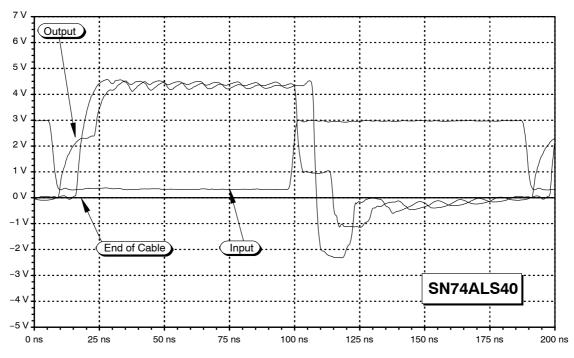

| 57     | Output Waveforms of the SN74ALS00     | 1–42 |

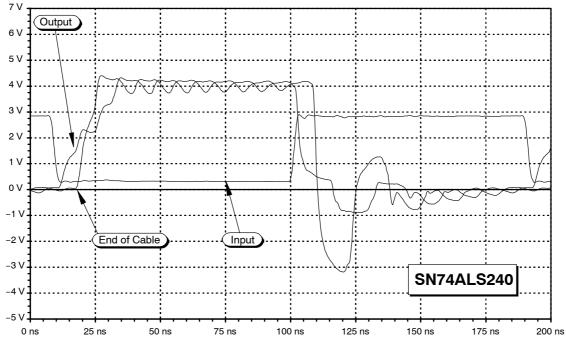

| 58     | Output Waveforms of the SN74ALS40     | 1-43 |

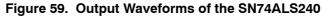

| 59     | Output Waveforms of the SN74ALS240    | 1-43 |

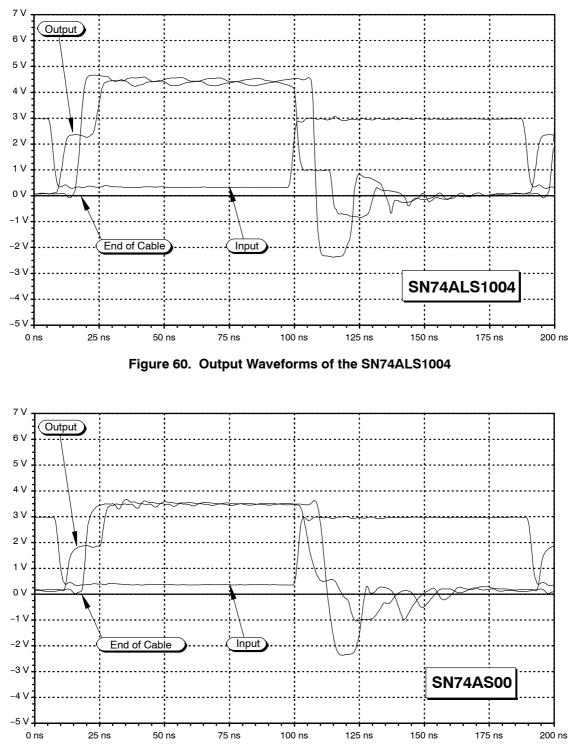

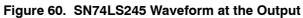

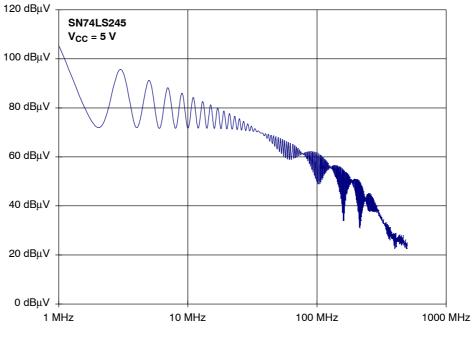

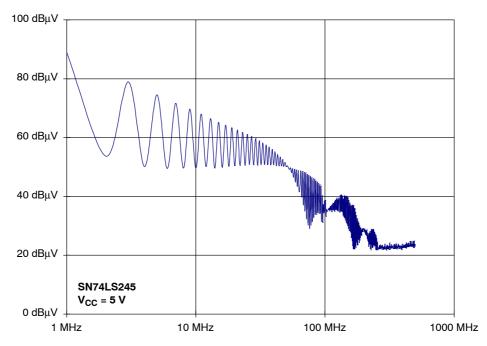

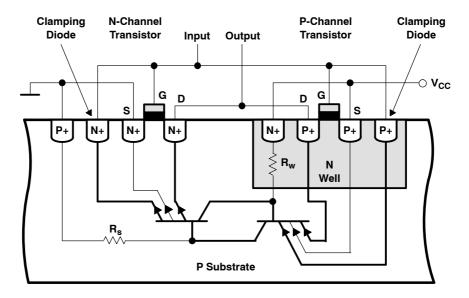

| 60     | Output Waveforms of the SN74ALS1004   | 1–44 |

| 61     | Output Waveforms of the SN74AS00      | 1–44 |

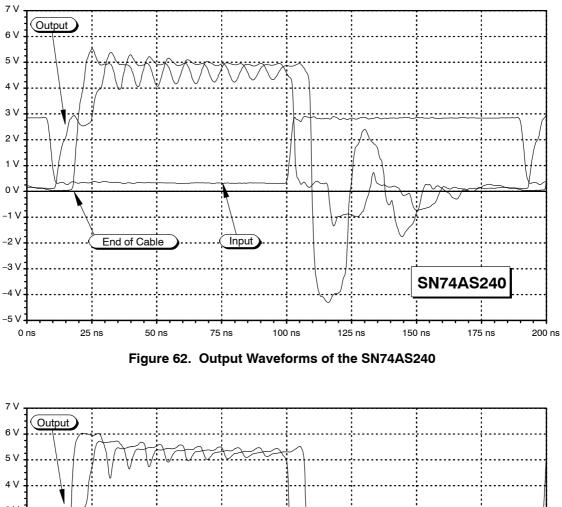

| 62     | Output Waveforms of the SN74AS240     | 1–45 |

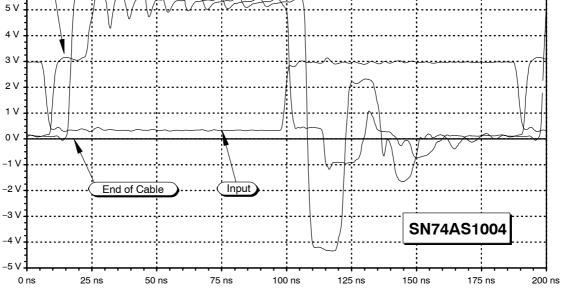

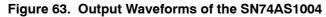

| 63     | Output Waveforms of the SN74AS1004    | 1–45 |

| 64     | Output Waveforms of the SN74F00       | 1-46 |

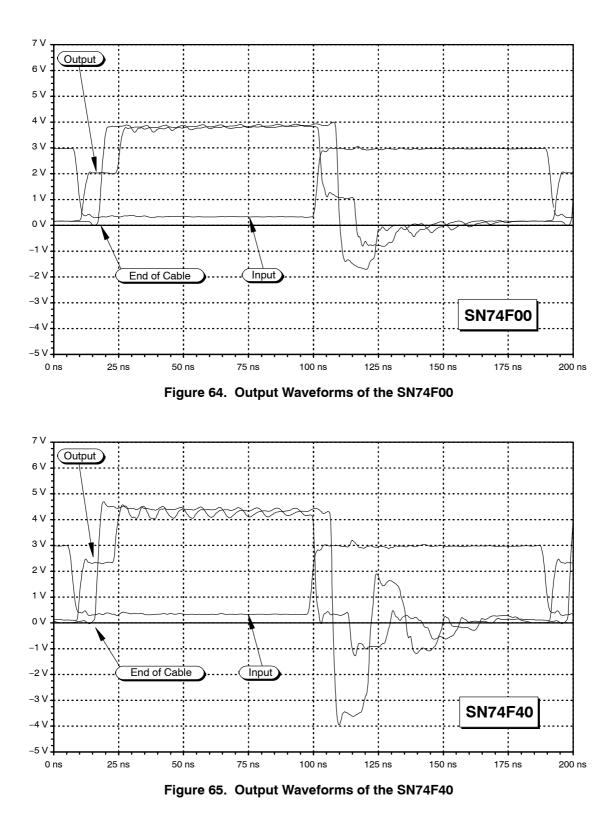

| 65     | Output Waveforms of the SN74F40       | 1–46 |

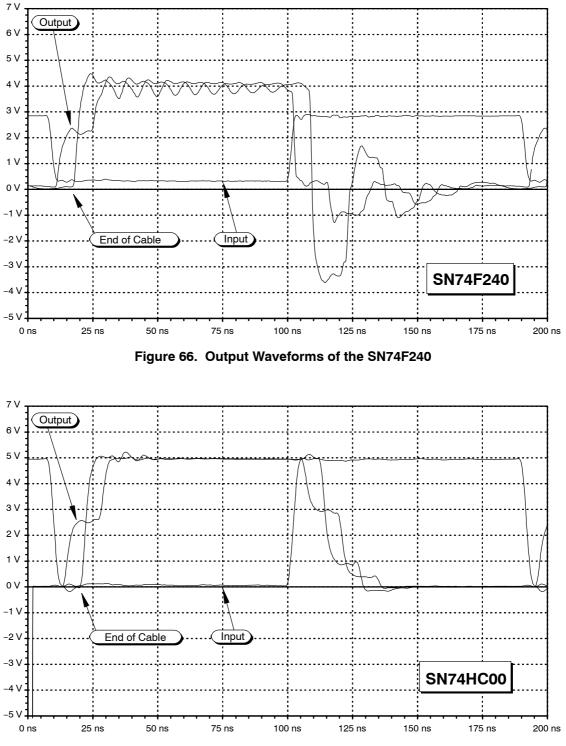

| 66     | Output Waveforms of the SN74F240      | 1–47 |

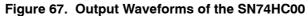

| 67     | Output Waveforms of the SN74HC00      | 1–47 |

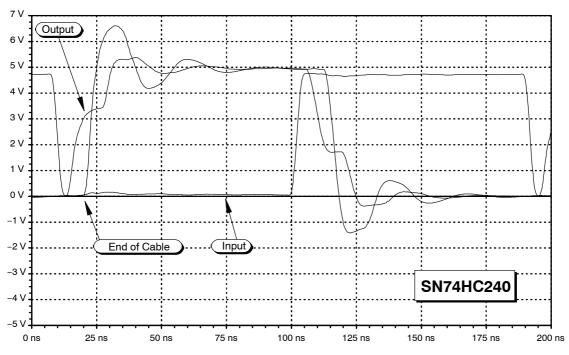

| 68     | Output Waveforms of the SN74HC240     | 1–48 |

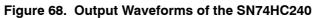

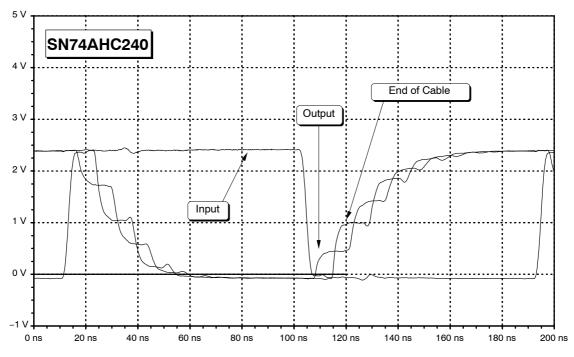

| 69     | Output Waveforms of the SN74AHC240    | 1–48 |

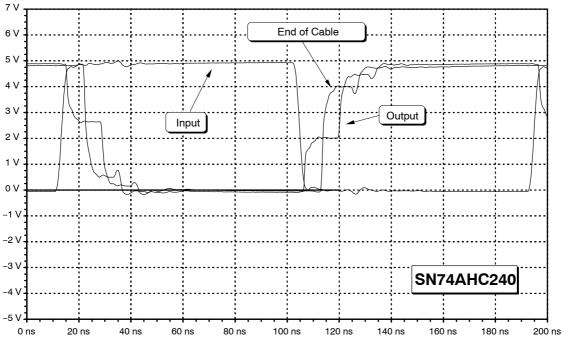

| 70     | Output Waveforms of the SN74AC240     | 1–49 |

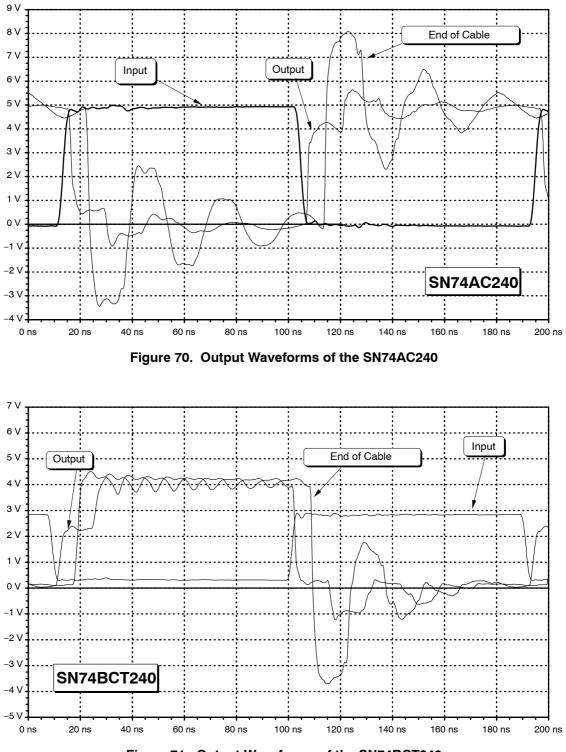

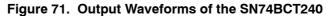

| 71     | Output Waveforms of the SN74BCT240    | 1–49 |

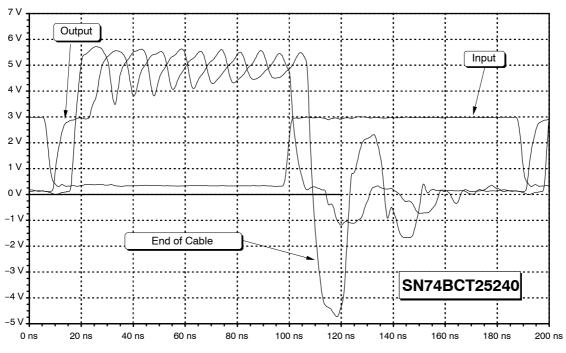

| 72     | Output Waveforms of the SN74BCT25240  | 1–50 |

| 73     | Output Waveforms of the SN74ABT240    | 1–50 |

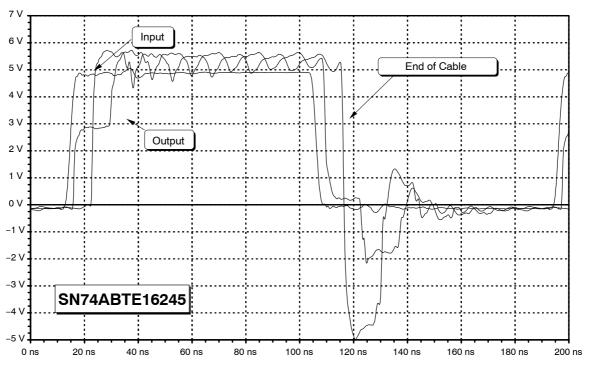

| 74     | Output Waveforms of the SN74ABTE16245 | 1–51 |

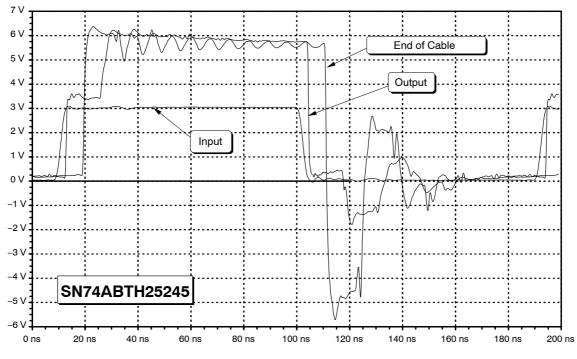

| 75     | Output Waveforms of the SN74ABTH25245 | 1–51 |

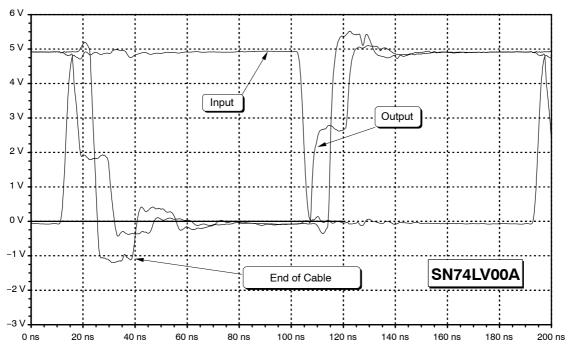

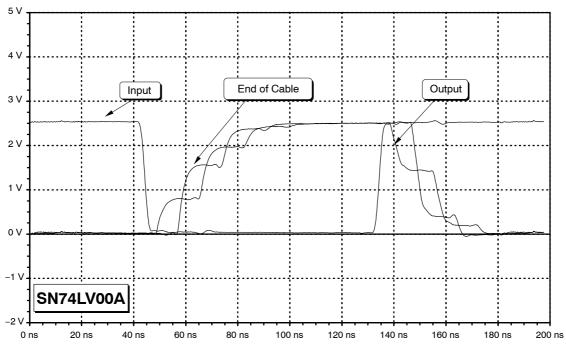

| 76     | Output Waveforms of the SN74LV00A     | 1–52 |

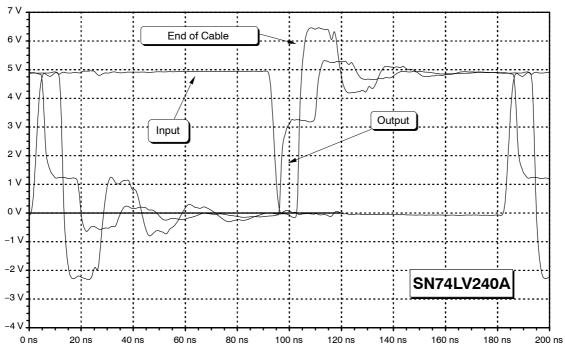

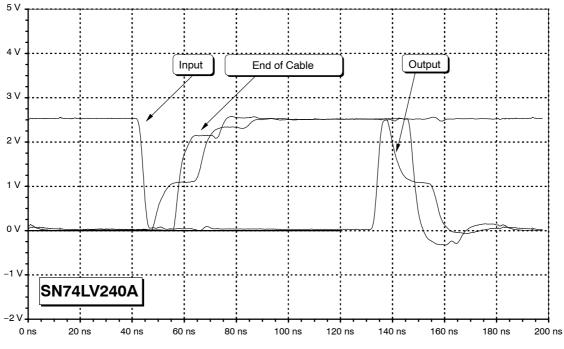

| 77     | Output Waveforms of the SN74LV240A    | 1–52 |

### Abstract

This application report presents a comprehensive collection of the input and output characteristic curves of integrated circuits from various 5-V logic families. These curves go beyond the information given in data sheets by providing additional details regarding the characteristics of the components. This knowledge is particularly useful when, for example, a decision must be made as to which circuit should be used in a bus system, or when the waveforms that can be expected in a transmission system need to be predicted by using a Bergeron chart. These oscillograms are of great assistance when generating models for simulation programs, which analyze the dynamic behavior of the integrated circuits in a particular environment.

### 1 Introduction

The parameters given in the data sheets of integrated circuits can give only a very limited indication of their actual behavior in a system. Generally, data sheets give only information regarding the behavior over the input and output voltage range of 0 to 5 V. Even the output currents specified over this range only provide an incomplete picture of the actual performance that can be expected.

But, often the behavior outside the normal operating conditions is of interest. This is, for example, the situation when the characteristic curves are used to predict the signal waveforms resulting from line reflections.

With the input/output (I/O) characteristics, use of the Bergeron method, and knowledge of the load resistor, the amplitude of the line reflections can be determined.

This application report contains the input and output characteristics of integrated logic circuits, operating at  $V_{CC} = 5$  V.

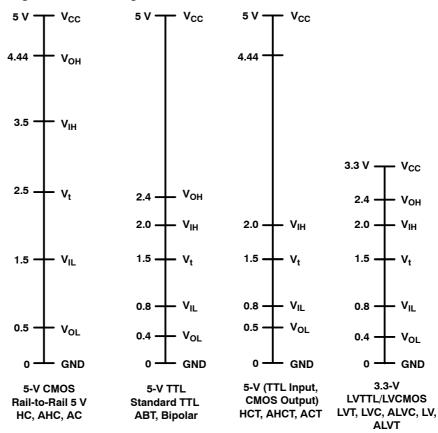

Many modern logic families are specified for operation at different supply voltages. For example, the AHC logic can be used at 5-V, 3.3-V, or even at 2.5-V supply voltage.

Since three supply voltages are currently used, it is necessary to provide I/O characteristics at these different voltage levels. This report deals exclusively with devices operated at  $V_{CC} = 5$  V.

Two other application reports regarding this topic are available:

- Input and Output Characteristics of Digital Integrated Circuits at 3.3-V Supply Voltage, literature number SZZA010

- Input and Output Characteristics of Digital Integrated Circuits at 2.5-V Supply Voltage, literature number SZZA012

In view of the wide range of integrated circuits available, it is necessary to limit this information to typical characteristics only.

In Sections 2 and 3 of this report, the input and output characteristics of the following circuits are representative of other components that behave similarly in circuits:

- '00 The characteristic curves of this NAND gate are representative of all logic circuits having normal drive capability, such as gates, flip-flops, counters, multiplexers, etc.

- <sup>'40</sup> For a range of applications, gates are available in several logic families having increased drive capability. Such components can supply about three times the output current, when compared with the normal drive capability of the logic circuits mentioned above.

- '1004 A special group of driver circuits introduced into the ALS and AS family for applications require a very large output current. These components play a particularly significant role in clock-distribution systems.

- <sup>2240</sup> The output characteristics of these bus-interface circuits are of particular importance when choosing a circuit family for a specific system requirement. As mentioned elsewhere in this report, the available output current has a decisive influence on the distortion of signals on bus lines.

- <sup>225240</sup> The incident wave switching (IWS) driver was developed to meet the requirements imposed by fast bus systems and applications with exceptionally low-resistance lines. Because these components play a very significant role in applications of this kind, their characteristic curves also have been included.

Table 1 gives an overview of the input and output characteristics, which are shown in Figures 1 through 77 in the remaining sections of this application report.

Because input characteristics depend exclusively on the technology used, rather than on the logical function of the device, only one representation per logic family is shown (gate function '00 or driver function '240) in the input-characteristics section.

|                       | ТҮРЕ         |              |                  |              |            |  |

|-----------------------|--------------|--------------|------------------|--------------|------------|--|

| FAMILY                | '00          | '40          | '240/'244        | '1004        | '25240     |  |

| SN74                  | $\checkmark$ | $\checkmark$ |                  |              |            |  |

| SN74LS                | $\checkmark$ | $\checkmark$ | $\checkmark$     |              |            |  |

| SN74S                 | $\checkmark$ | $\checkmark$ | $\checkmark$     |              |            |  |

| SN74ALS               | $\checkmark$ | $\checkmark$ | $\checkmark$     | $\checkmark$ |            |  |

| SN74AS                | $\checkmark$ |              | $\checkmark$     | $\checkmark$ |            |  |

| SN74F                 | $\checkmark$ | $\checkmark$ | $\checkmark$     |              |            |  |

| SN74HC                | $\checkmark$ |              | $\checkmark$     |              |            |  |

| SN74AHC               | $\checkmark$ |              | $\checkmark$     |              |            |  |

| SN74AC                | $\checkmark$ |              | $\checkmark$     |              |            |  |

| SN74BCT               |              |              | $\checkmark$     |              |            |  |

| SN74ABT <sup>†</sup>  |              |              | $\checkmark$     |              | $\sqrt{1}$ |  |

| SN74ABTE <sup>†</sup> |              |              | $\sqrt{\dagger}$ |              |            |  |

| SN74LV                | $\checkmark$ |              | $\checkmark$     |              |            |  |

Table 1. Representatives of the Different Logic Families

<sup>†</sup> For the ABT/ABTE families, the measurements were taken using the bidirectional devices SN74ABT25245 and SN74ABTE16245.

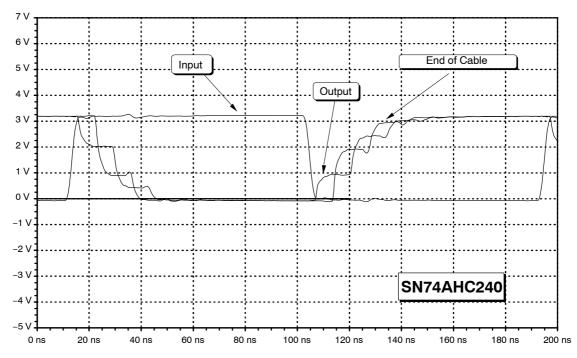

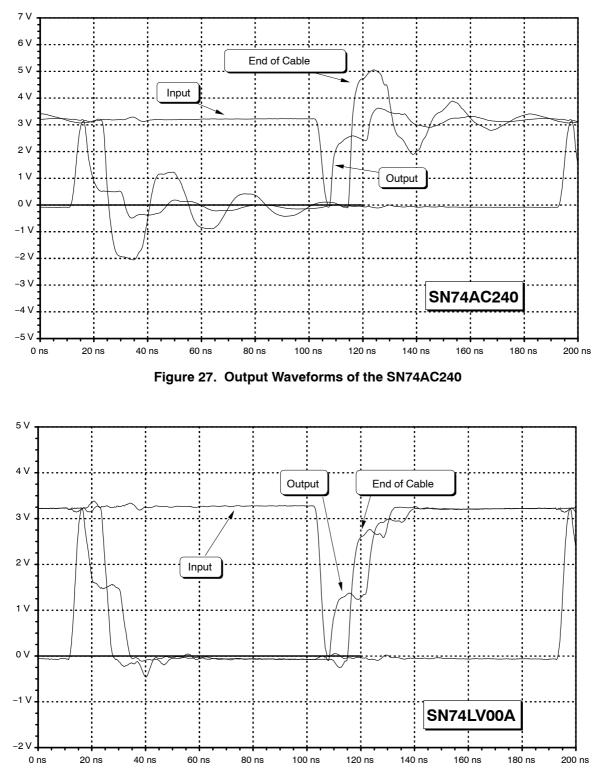

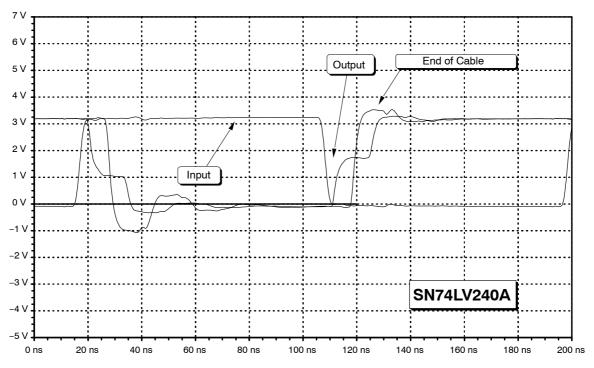

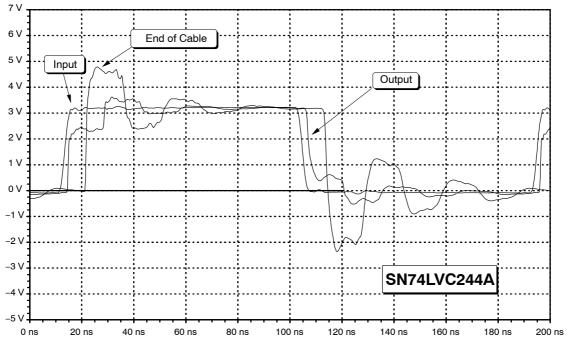

Section 4 contains the calculation of line reflections using the Bergeron method, based on the SN74AHC240 device. Measurement results, demonstrating different switching behaviors of the various logic families, are given in Section 5. For these measurements, the devices under test were loaded with a 1.3-m-long coaxial cable having a characteristic impedance of 50  $\Omega$ . The end of the cable was not connected, i.e., open circuit. These waveforms provide good insight into the dynamic behavior of the components.

### 2 Input Characteristics

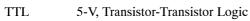

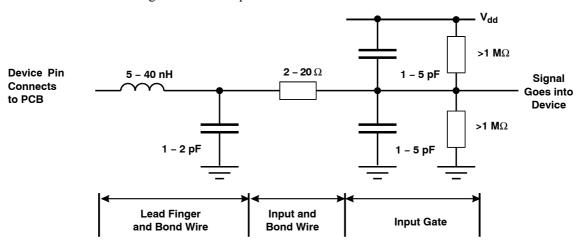

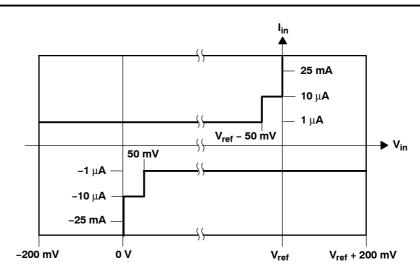

In the positive range, the high impedance of the input stage of the logic circuit determines the input characteristics of logic circuits (see Figures 1 through 12).

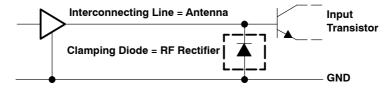

For bipolar circuits, a base-emitter current, which flows into the input circuitry, is needed. Therefore, the input resistance for bipolar logic devices is in the range of several kilohms. Negative voltage peaks are limited by a protection diode.

CMOS and BiCMOS circuits have CMOS inputs. The CMOS input stages are exclusively controlled by the applied voltage, so there is no current flowing into the input stage. Therefore, the input impedance of CMOS and BiCMOS devices is much higher and is in the range of megohms. Again, negative voltage peaks are limited by a protection diode.

The input stages of some CMOS logic families (SN74HC, SN74AC) also have an input protection diode, that is connected to  $V_{CC}$ . This diode limits the positive input voltage to maximum  $V_{CC}$  + 0.7 V.

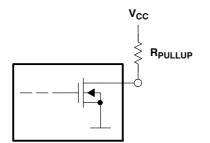

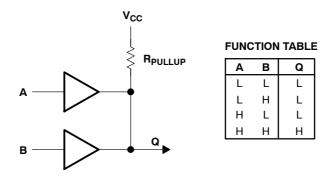

The bus-hold circuit is a special input circuit that is an option for many ABT devices. Inputs of devices that have the bus-hold circuit hold the last valid logic state. This feature is suitable where an input remains undefined, e.g., during a high-impedance state on the bus. Using the bus-hold circuit eliminates the need for pullup or pulldown resistors.

Devices with the bus-hold circuit are designated by an H in their nomenclature, for example, SN74ABTH245.

A more detailed application report, *Bus-Hold Circuits*, literature number SZDAE15, is available from Texas Instruments  $(TI^{TM})$ .

Additional application reports and other related literature are listed in Section 7, References.

Figure 1. Input Characteristic of the SN74xxx Series

Figure 5. Input Characteristic of the SN74ASxxx Series

Figure 7. Input Characteristic of the SN74HCxxx Series

Figure 9. Input Characteristic of the SN74ACxxx Series

Figure 11. Input Characteristic of the SN74ABTxxx Series

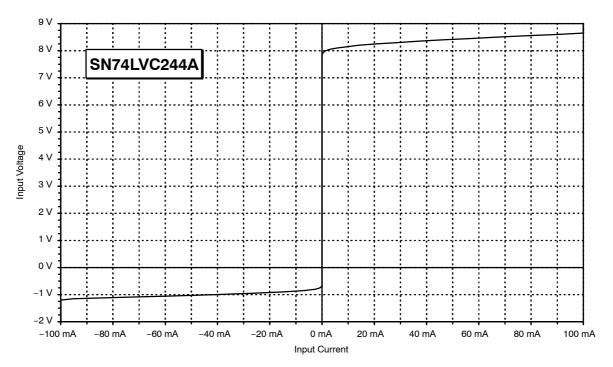

Figure 12. Input Characteristic of the SN74LVxxx Series

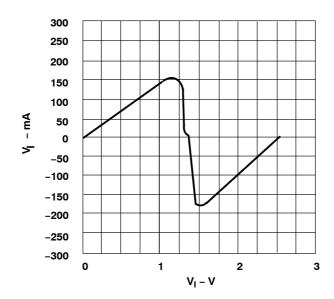

# **3 Output Characteristics**

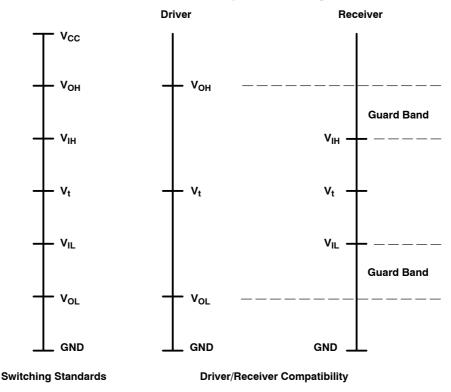

The output stage of a logic circuit in the high state behaves like a voltage source with an open circuit voltage of 5 V for CMOS logic, and 3.6 V for TTL and BiCMOS logic (see Figures 13 through 43). The internal resistance for the high state is inversely proportional to the drive capability of the device. The value of the internal resistance for the standard logic families is in the range of 30  $\Omega$  to 40  $\Omega$ . The internal resistance of the IWS driver is lower than 5  $\Omega$ .

In the low state, for positive voltages, the output resistance is based on the internal resistance of the conducting transistor, i.e., collector-emitter for bipolar and BiCMOS technologies and drain-source resistance for CMOS technologies. Again, negative voltage peaks are limited by a protection diode.

The output stages of some CMOS logic families (SN74HC, SN74AC) also have an input protection diode, which is connected to  $V_{CC}$ . This diode limits the positive input voltage to maximum  $V_{CC} + 0.7$  V.

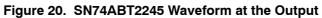

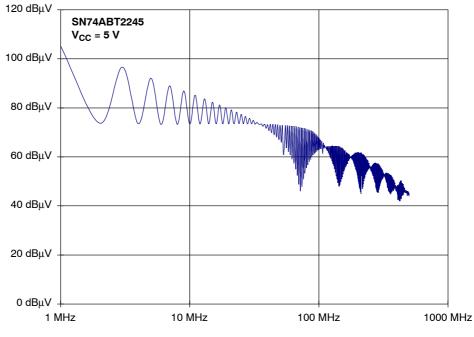

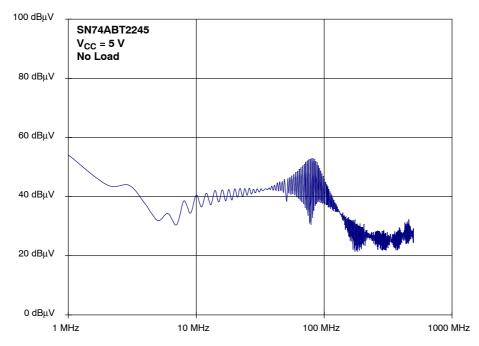

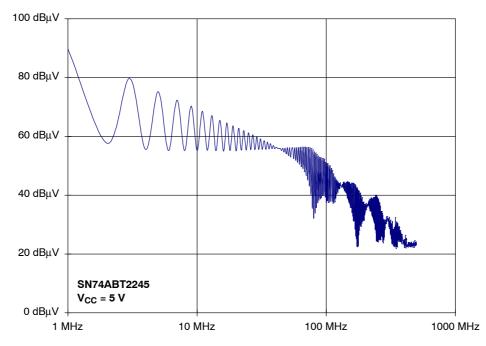

TI offers driver options in the ABT family with integrated series resistors rated at about 25  $\Omega$ .

Using the damping resistors at the output stage, the effective output impedance of the driver is about 30  $\Omega$ . If the value of the line impedance also is about 30  $\Omega$ , no line reflections will be observed at the output of the device. In this case, the beginning of the line is terminated perfectly.

This option is especially beneficial for memory applications. In those applications, overshoots and undershoots may cause malfunctions. In point-to-point applications, nearly ideal signal shapes can be achieved. The 2 following the alphabetical part of the device number indicates the series damping resistor, for example, SN74ABT2245.

Further information on the topic of series damping resistors is given in the TI application report, *Bus-Interface Devices With Output-Damping Resistors or Reduced-Drive Outputs*, literature number SCBA012A.

More application reports and other related literature are listed in Section 7, References.

Figure 13. Output Characteristic of the SN7400

Figure 15. Output Characteristic of the SN74LS00

Figure 19. Output Characteristic of the SN74S40

Figure 23. Output Characteristic of the SN74ALS240

Figure 27. Output Characteristic of the SN74AS1004

Figure 31. Output Characteristic of the SN74HC00

Figure 33. Output Characteristic of the SN74AHC00

Figure 35. Output Characteristic of the SN74AC00

Figure 37. Output Characteristic of the SN74BCT240

Figure 39. Output Characteristic of the SN74ABT240

Figure 41. Output Characteristic of the SN74ABT25245

Figure 43. Output Characteristic of the SN74LV240A

# 4 Bergeron Method Applied to the SN74AHC240

The input and output characteristics, shown in Section 1, *Introduction*, and Section 3, *Output Characteristics*, can be used to determine the signal reflections within a certain application using a graphical procedure known as the Bergeron method.

The prerequisite to using the Bergeron method is that the lines must exceed a certain length. There is a simple rule:

If the rise time or the fall time of a signal is shorter than twice the propagation delay on the line, the line theories must be applied.

Practically, this means that for a line with a signal propagation time of 5 ns/m and a signal with a rising or falling edge of 2 ns, starting with a line length that exceeds 20 cm  $[2 \text{ ns} / (5 \text{ ns/m} \times 2)]$ , the line theory must be applied.

For a bus line, the signal propagation delay increases to 25 ns/m, so that, in this case, the line theory must be applied for a line that exceeds 4 cm  $[2 \text{ ns} / (25 \text{ ns/m} \times 2)]$

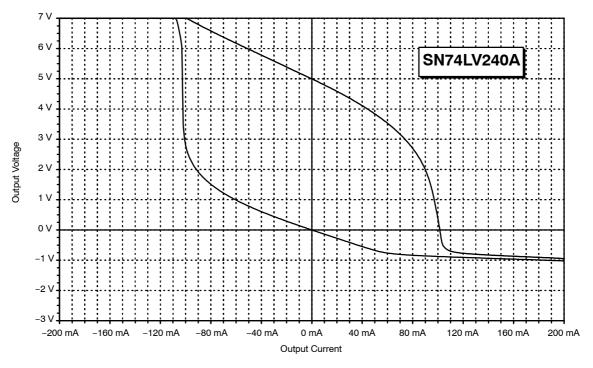

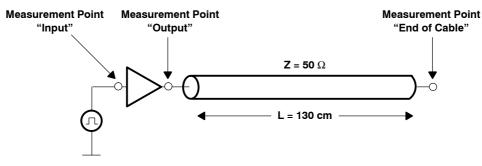

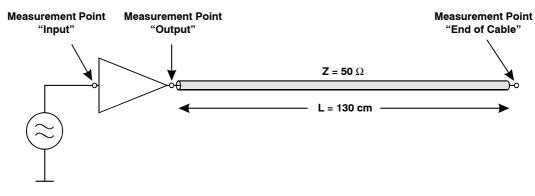

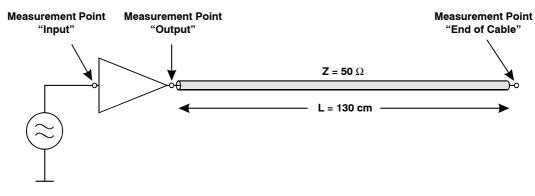

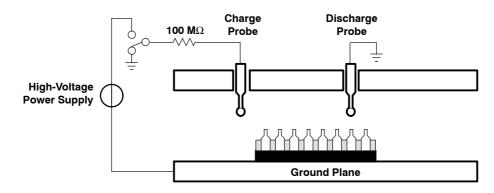

In the example, the SN74AHC240 device was tested. The Bergeron method was used to determine the signal shape in advance. The measurement setup is shown in Figure 44.

Practically, this means, that for a line with a signal propagation of 5 ns/m and a signal with a rising or falling edge of 2 ns, starting with a line length that exceeds 20 cm  $[2 \text{ ns} / (5 \text{ns/m} \times 2)]$ , the line theory must be applied.

For a bus line, the signal propagation delay increases to 25 ns/m, so that, in this case, the line theory must be applied for a line length that exceeds 4 cm  $[2 \text{ ns} / (25 \text{ ns/m} \times 2)]$ .

In the example, the SN74AHC240 device was tested. The Bergeron method was used to determine the signal shape in advance. The measurement setup is shown in Figure 44.

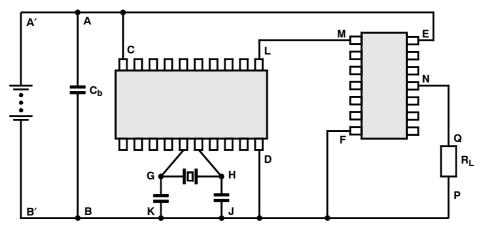

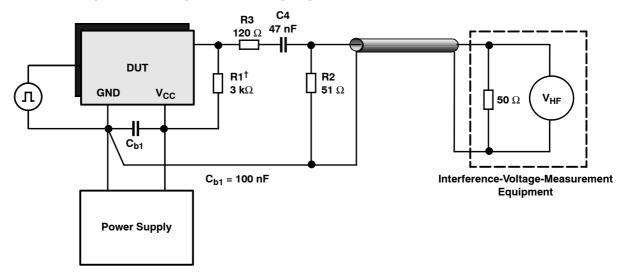

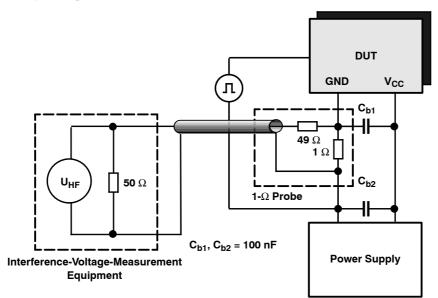

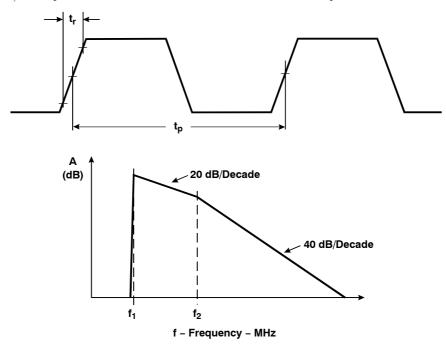

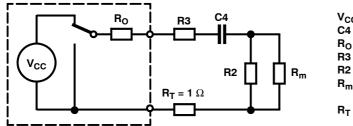

Figure 44. Measurement Setup for the Bergeron Method

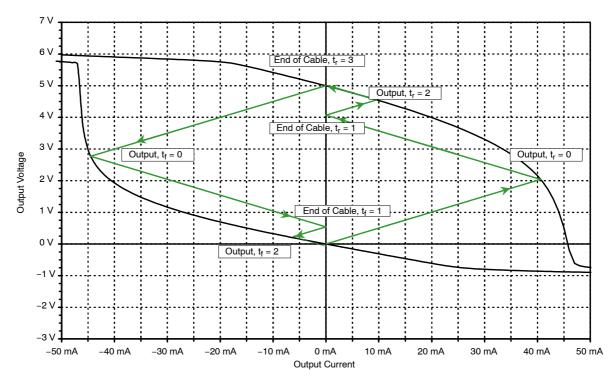

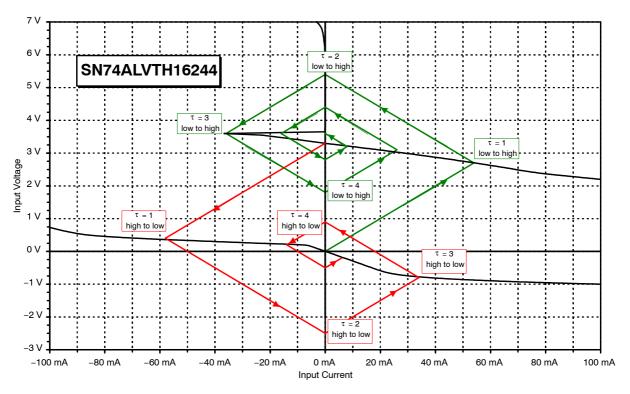

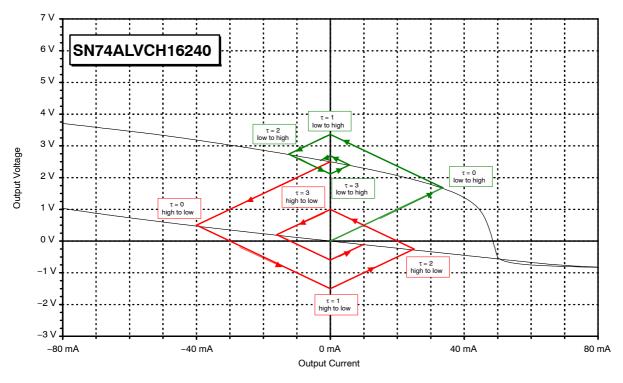

The first step in doing the graphical solution using the Bergeron method is to draw the output and load characteristics in a voltage-versus-current diagram:

- Output characteristic of the device SN74AHC240

- Load characteristic at the end of the line

The output characteristic is taken directly from Figure 45. The load characteristic equals the Y-axis for the investigated case, because no resistor is connected to the end of the line ( $R_L = \infty$ ).

The intersection between the load characteristic and the output characteristic represents the steady states and the current and voltage values at the line start and the end of the line at the time t < 0, respectively.

### 4.1 Voltage Value at the Output of the Driver

For the low-to-high transition, a straight line is drawn, starting at the intersection of the output low characteristic and the load characteristic. For the high-to-low transition, the straight line starts at the cross point of output high characteristic and the load characteristic.

The line impedance,  $Z_{\Omega}$ , determines the steepness of this line. In the example, the line impedance is 50  $\Omega$ .

The intersection of this straight line and the output characteristics gives the voltage and current values at the beginning of the line at the time t = 0.

#### 4.2 Voltage Value at End of the Line

Now, a straight line with the steepness  $-Z_0$  is drawn through this point. The intersection between this line and the load characteristic gives the voltage values at the end of the line after one propagation delay time of the line, that is after time t = 1.

Afterwards, the procedure will be repeated, applying straight lines to the output characteristic and the load characteristic.

The steepness of the straight line is:

- Z<sub>0</sub> from the output characteristic to the load characteristic and

- -Z<sub>0</sub> from the load characteristic to the output characteristic.

In this way, the current/voltage values are determined:

- at the end of the line, at the times  $t = 1, 3, 5 \dots$

- at the beginning of the line, at the times t = 2, 4, 6...

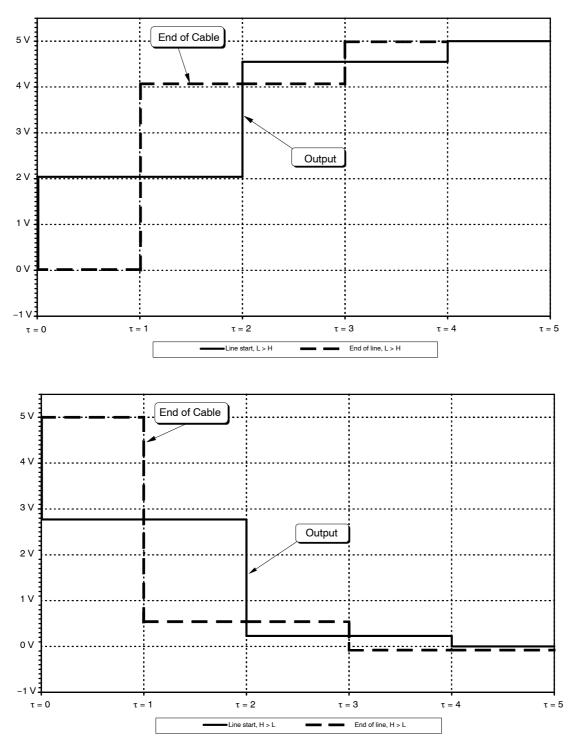

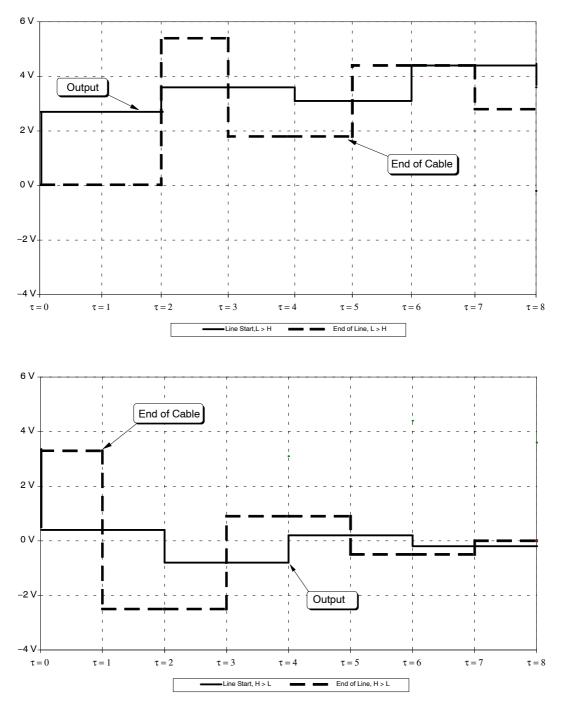

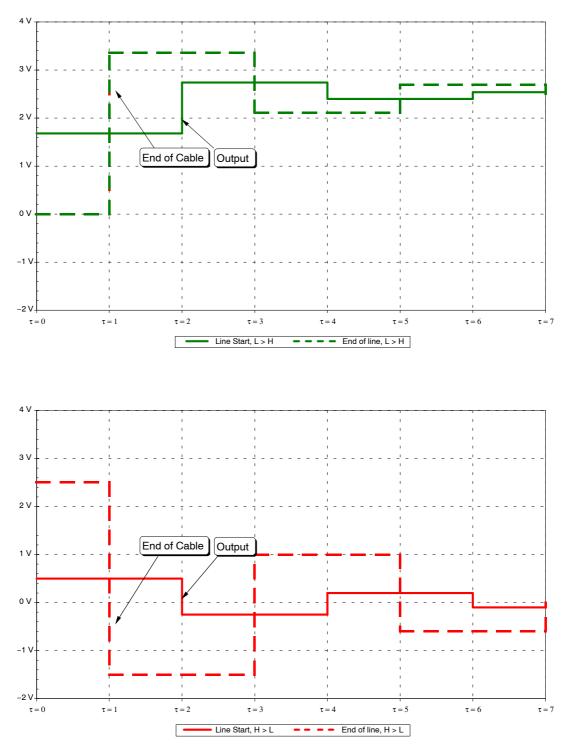

The Bergeron diagram is shown in Figure 45. The related diagram, which shows the line reflections, is shown in Figure 46.

Figure 45. Bergeron Diagram for the SN74AHC240

Figure 46. Diagram of Line Reflections for the SN74AHC240

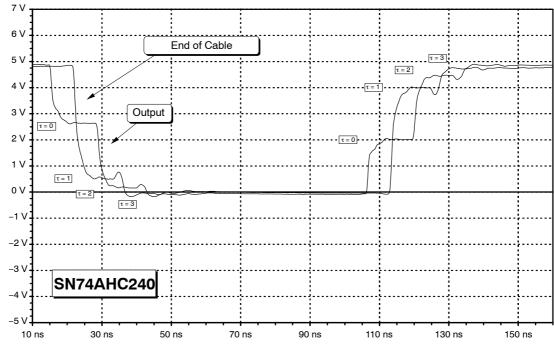

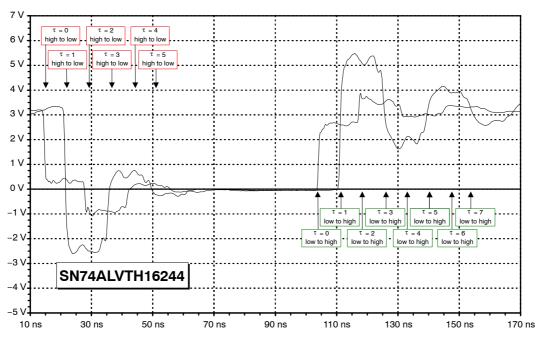

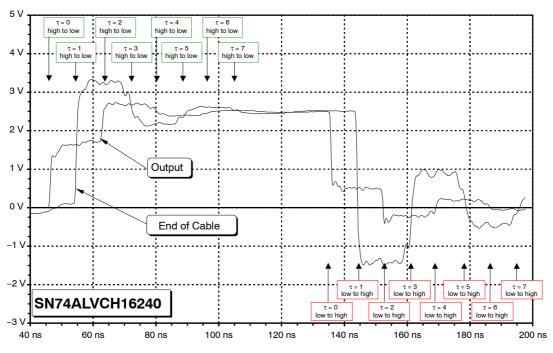

Figure 47 shows the line-reflection measurement results for the SN74AHC240.

The calculated values using the Bergeron procedure match very well with the measurement of the signal shapes. The TI application report, *The Bergeron Method: A Graphic Method for Determining Line Reflections in Transient Phenomena*, literature number SDYA014, describes the graphic procedure in more detail.

#### **5 Output Waveforms**

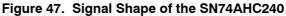

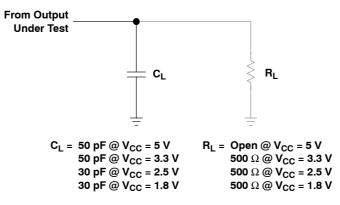

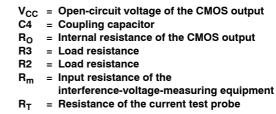

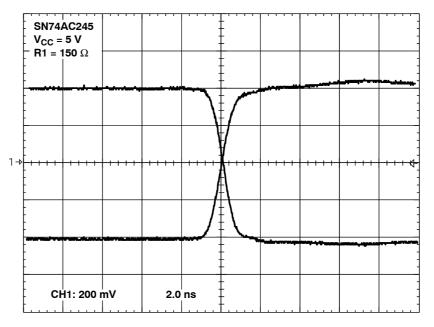

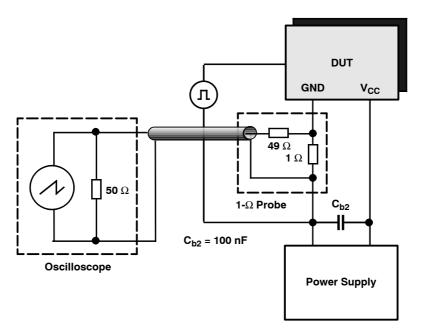

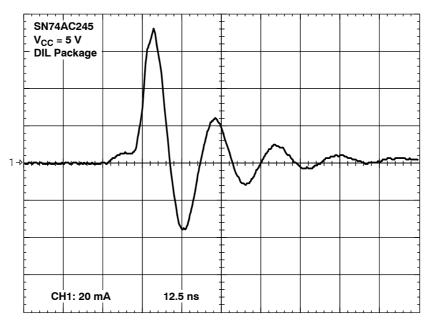

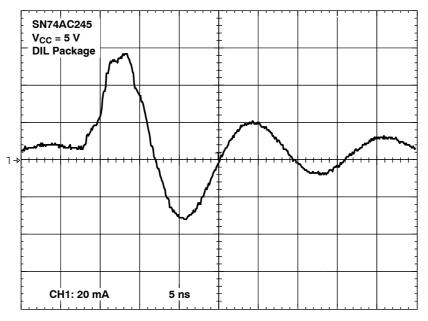

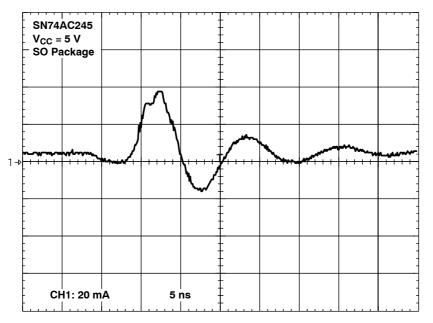

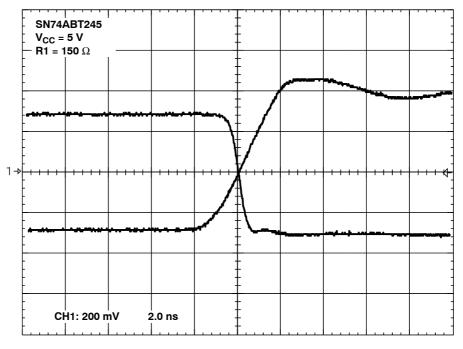

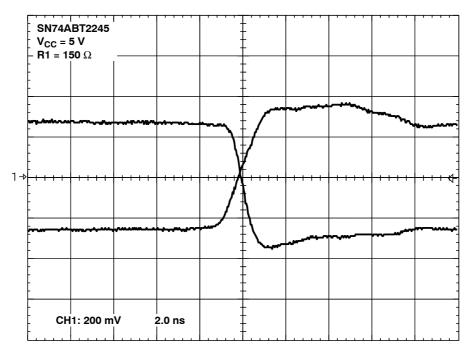

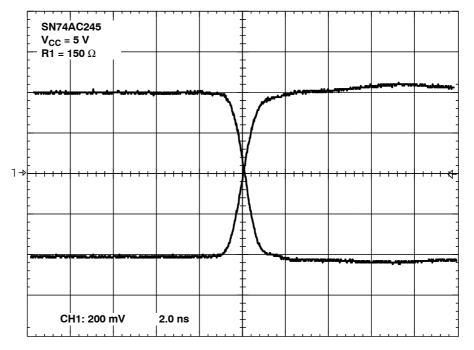

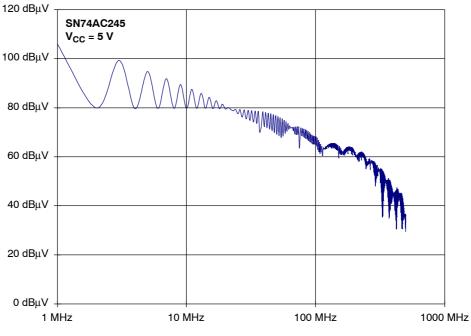

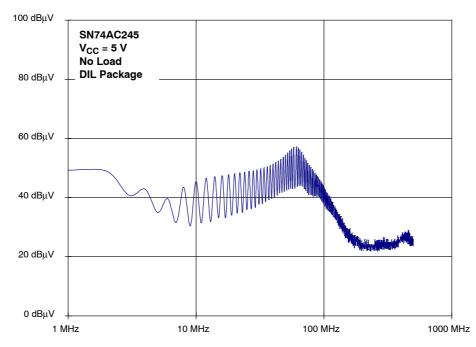

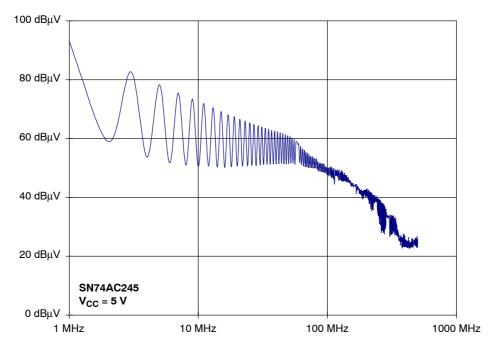

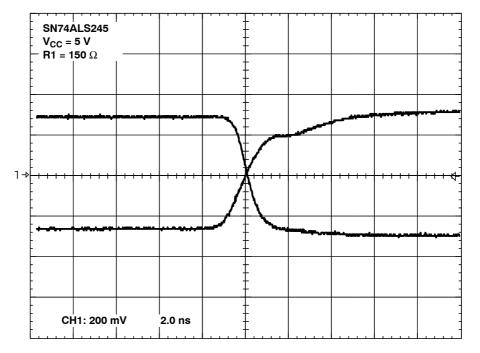

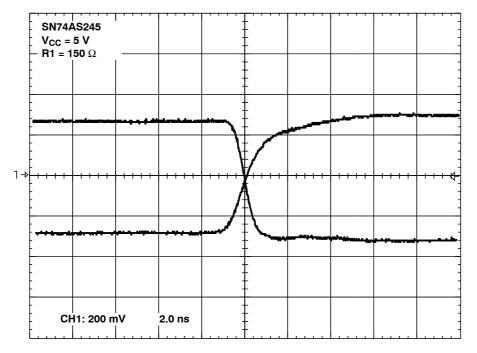

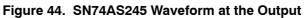

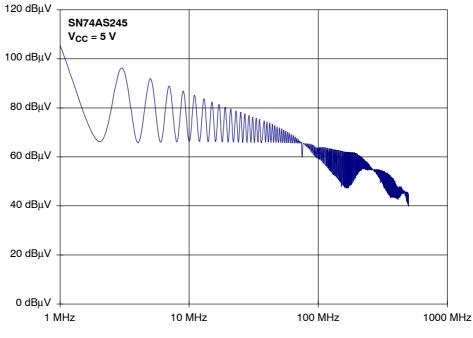

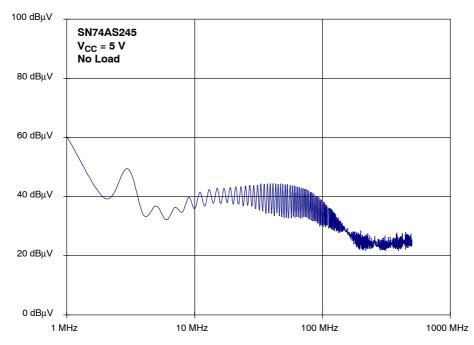

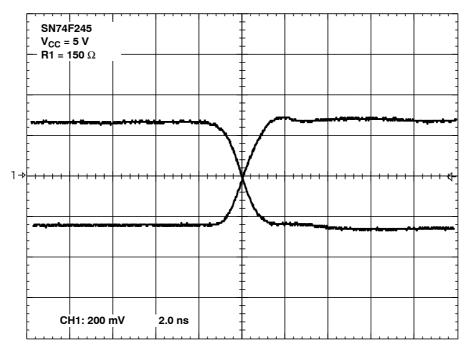

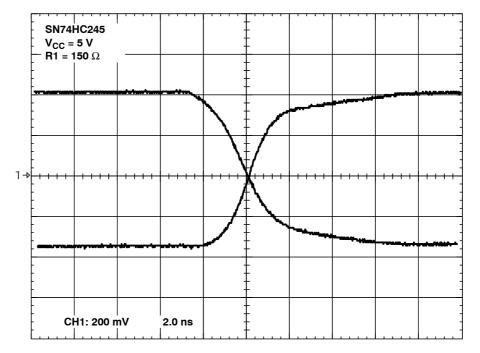

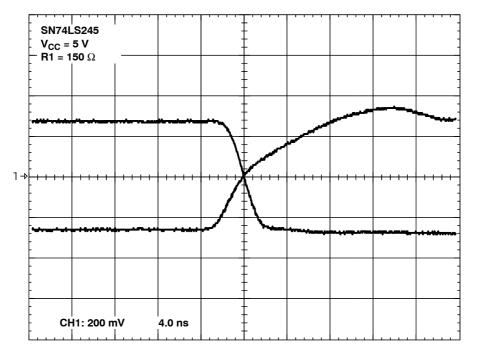

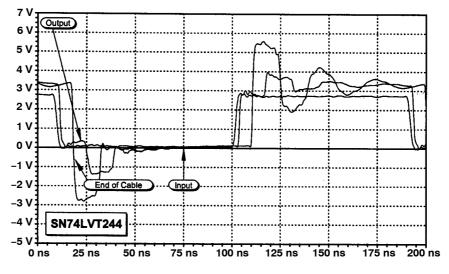

The measurement setup shown in Figure 48 is used to obtain the voltage waveforms of typical output stages (see Figures 49 through 77).

Figure 48. Measurement Setup for the Bergeron Method

For these measurements, the devices under test were loaded with a 1.3-m-long coaxial cable having a characteristic impedance of 50  $\Omega$ . The end of the line was not connected, i.e., open circuit.

These waveforms provide good insight into the dynamic behavior of the components. In particular, the oscillograms provide information regarding drive capability with a low-resistance load, together with an indication of the line reflections that can be expected.

Figure 49. Output Waveforms of the SN7400

Figure 51. Output Waveforms of the SN74LS00

Figure 54. Output Waveforms of the SN74S00

Figure 58. Output Waveforms of the SN74ALS40

Figure 74. Output Waveforms of the SN74ABTE16245

Figure 75. Output Waveforms of the SN74ABTH25245

## 6 Abbreviations and Glossary

## Α

- SN74AC Advanced CMOS

- SN74ABT Advanced BiCMOS Technology

- SN74AHC Advanced High-Speed CMOS

- SN74ALS Advanced Low-Power Schottky

- SN74AS Advanced Schottky

- SN74BCT BiCMOS Technology

- BiCMOS Combination of Bipolar and CMOS process (CMOS input structure, bipolar output structure)

| GND Gr | ound |

|--------|------|

|--------|------|

## Η

High-speed CMOS

Input/Output

- SN74LS Low-power Schottky

- SN74LV Low-Voltage CMOS, originally designed for  $V_{CC}$  = 3.3-V, also specified at 5 V

R<sub>L</sub> Load resistor

# S

| Schottky |

|----------|

|          |

SPICE Simulation Program with Integrated Circuit Emphasis

V<sub>CC</sub> Supply voltage

## **7** References

## 7.1 Documents Published by TI

ABT Logic Advanced BiCMOS Technology, Data Book, 1998, literature number SCBD002C.

Advanced CMOS Logic, Data Book, 1996, literature number SCADE02.

Logic Selection Guide and Data Book, CD-ROM, April 1998, literature number SCBC001B.

AHC/AHCT Logic Advanced High-Speed CMOS, Data Book, 1997, literature number SCLD003A.

Design Considerations for Logic, 1997, literature number SDYA002.

Digital Design Seminar, Reference Manual, 1998, literature number SDYDE01B.

Designing With Logic, March 1997, literature number SDYA009B.

*The Bergeron Method: A Graphic Method for Determining Line Reflections in Transient Phenomena*, October 1996, literature number SDYA014.

Bus-Interface Devices With Output-Damping Resistors or Reduced-Drive Outputs, August 1997, literature number SCBA012A.

Live Insertion, October 1996, literature number SDYA012.

Thin Very Small-Outline Package (TVSOP), March 1997, literature number SCBA009C.

Low-Voltage Logic Families, April 1997, literature number SCVAE01A.

Bus-Hold Circuit, July 1992, literature number SDZAE15.

Electromagnetic Emission from Logic Circuits, November 1998, literature number SZZA007.

PCB Design Guidelines for Reduced EMI, November 1998, literature number SZZA009.

Input and Output Characteristics of Digital Integrated Circuits at 3.3-V Supply Voltage, literature number SZZA010.

Input and Output Characteristics of Digital Integrated Circuits at 2.5-V Supply Voltage, literature number SZZA012.

## 7.2 Internet Information Sources

TI Semiconductor Home Page

http://www.ti.com/sc

#### **TI Distributors**

http://www.ti.com/sc/docs/distmenu.htm

#### TI Logic Home Page

http://www.ti.com.sc/docs/asl/lit/lit.htm

#### **TI Logic Literature**

http://www.ti.com/sc/docs/asl/lit/lit.htm

#### TI Product Information and Document Search

http://www.ti.com/sc/docs/msp/download.htm

## 8 Acknowledgment

The author of this document is Peter Forstner. Revisions were made by Johannes Huchzermeier.

# Input and Output Characteristics of Digital Integrated Circuits at 3.3-V Supply Voltage

SZZA010 September 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

## Contents

| Title |

|-------|

|-------|

|   | Title                                                                                                                                                                      | Page |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| A | bstract                                                                                                                                                                    | 1-61 |

| 1 | Introduction                                                                                                                                                               | 1-61 |

| 2 | Input Characteristics                                                                                                                                                      | 1-63 |

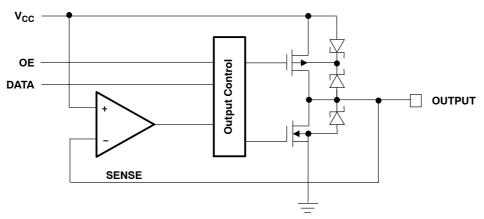

| 3 | Output Characteristics         3.1 Series Damping Resistors (SN74XXX2xxx, SN74XXXR2xxx)         3.2 Automatic High-Impedance State (Auto3-state) Output of the ALVT Family | 1-68 |

| 4 | Bergeron Method Applied to the SN74ALVTH16244         4.1 Voltage Value at the Output of the Driver         4.2 Voltage Value at End of the Line                           | 1-75 |

| 5 | Output Waveforms                                                                                                                                                           | 1-79 |

| 6 | Abbreviations and Glossary                                                                                                                                                 | 1-84 |

| 7 | References         7.1 Documents Published by TI         7.2 Internet Information Sources                                                                                  | 1-86 |

| 8 | Acknowledgment                                                                                                                                                             | 1-86 |

## List of Illustrations

| Figure | Title                                           | Page |

|--------|-------------------------------------------------|------|

| 1      | Input Characteristic of the SN74AHCxxx Series   | 1-63 |

| 2      | Input Characteristic of the SN74ACxxx Series    | 1–64 |

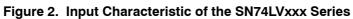

| 3      | Input Characteristic of the SN74LVxxx Series    | 1-64 |

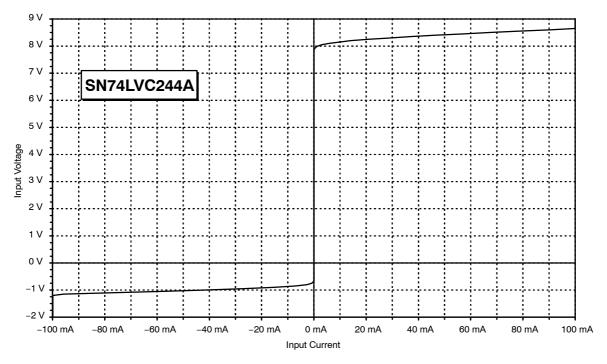

| 4      | Input Characteristic of the SN74LVCxxx Series   | 1-65 |

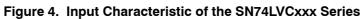

| 5      | Input Characteristic of the SN74ALVCxxx Series  | 1-65 |

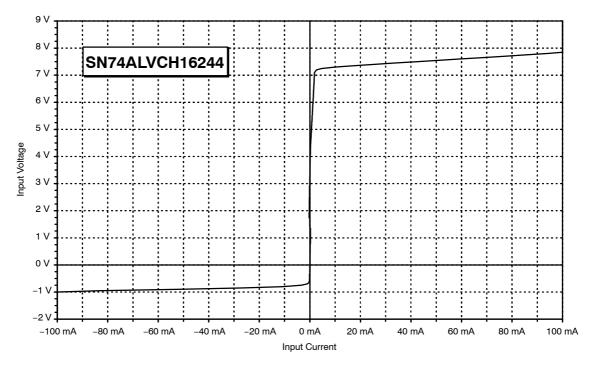

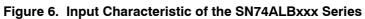

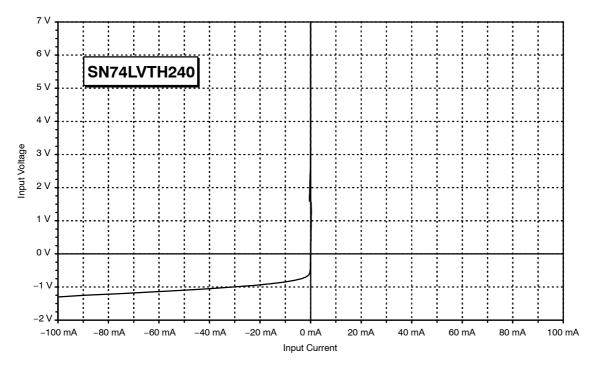

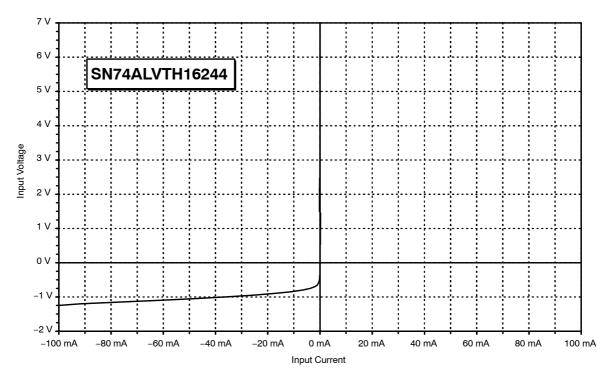

| 6      | Input Characteristic of the SN74ALBxxx Series   | 1-66 |

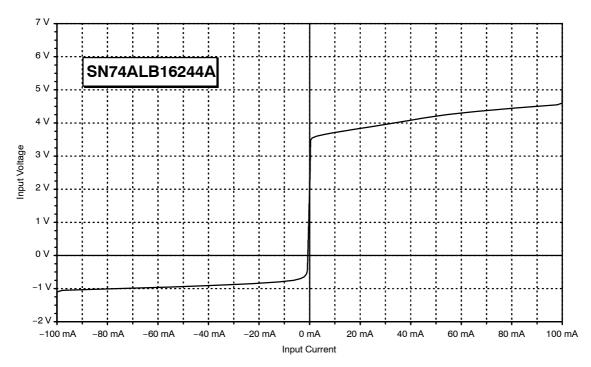

| 7      | Input Characteristic of the SN74LVTHxxx Series  | 1–66 |

| 8      | Input Characteristic of the SN74ALVTHxxx Series | 1-67 |

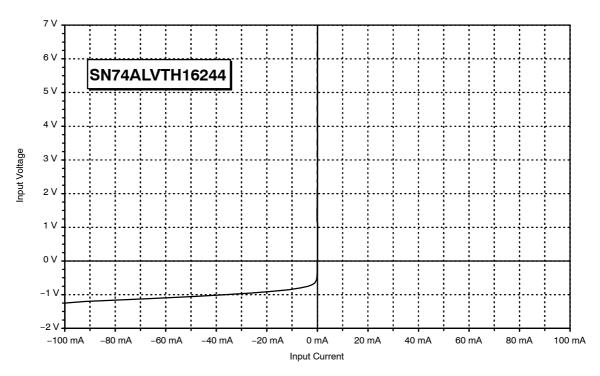

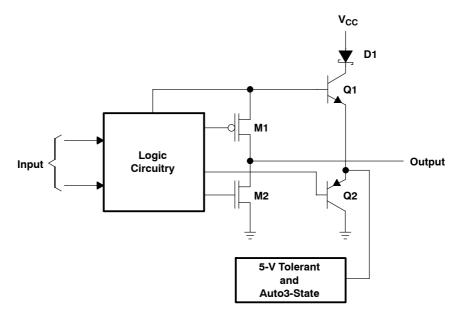

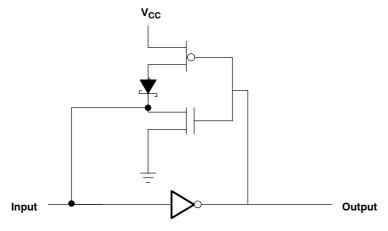

| 9      | Simplified Output Stage of ALVT Devices         | 1-68 |

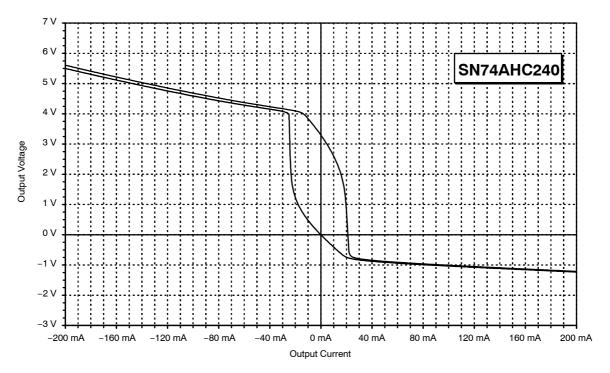

| 10     | Output Characteristics of the SN74AHC00         | 1-69 |

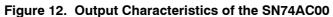

| 11     | Output Characteristics of the SN74AHC240        | 1–69 |

| 12     | Output Characteristics of the SN74AC00          | 1-70 |

| 13     | Output Characteristics of the SN74AC240         | 1-70 |

| 14     | Output Characteristics of the SN74LV00A         | 1–71 |

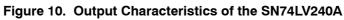

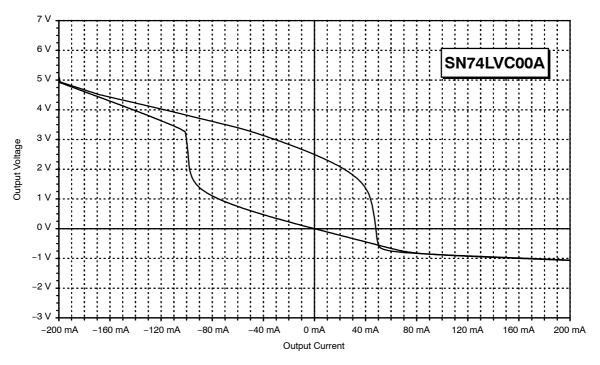

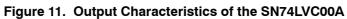

| 15     | Output Characteristics of the SN74LV240A        | 1–71 |

## List of Illustrations (Continued)

| Title                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

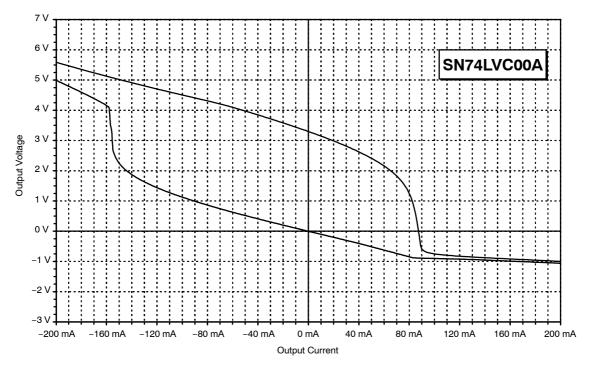

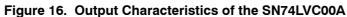

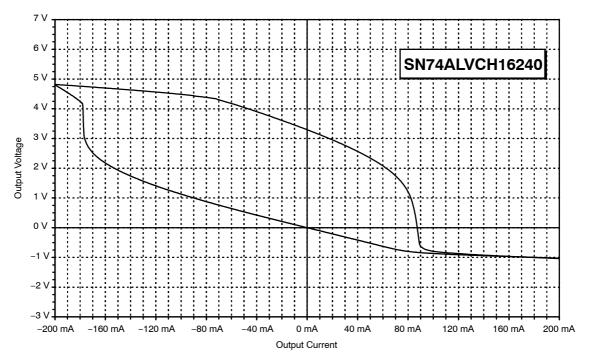

| Output Characteristics of the SN74LVC00A           | 1–72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

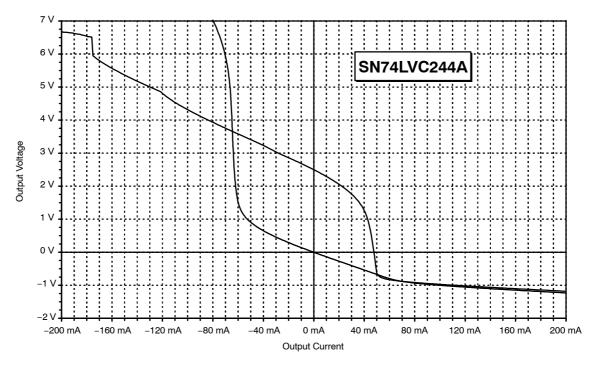

| Output Characteristics of the SN74LVC240A          | 1–72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

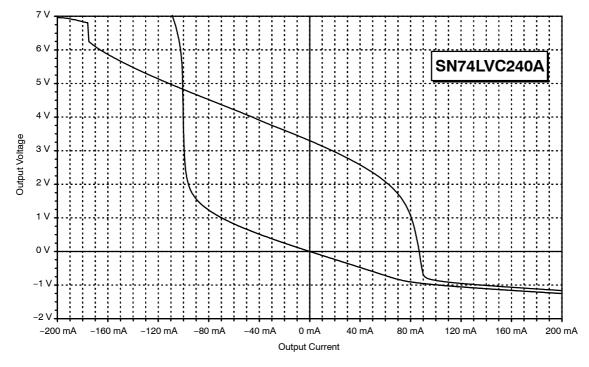

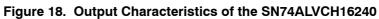

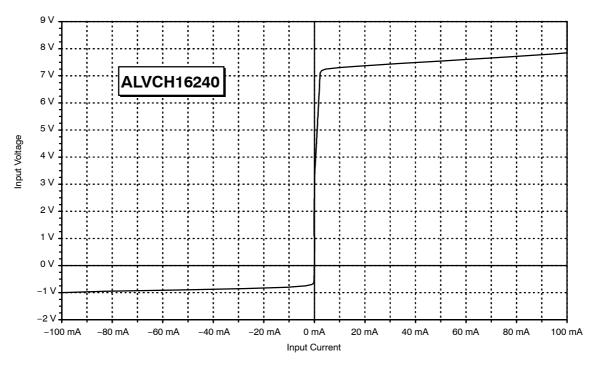

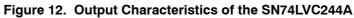

| Output Characteristics of the SN74ALVCH16240       | 1–73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

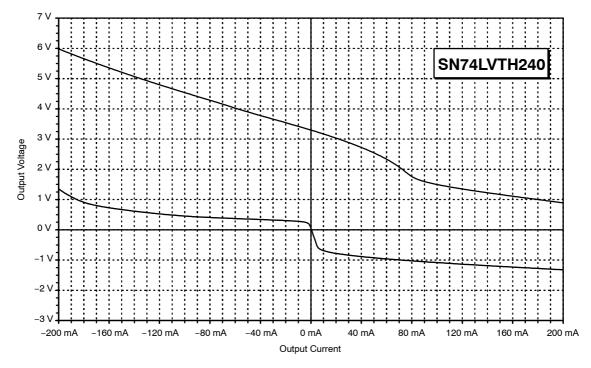

| Output Characteristics of the SN74LVTH240          | 1–73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

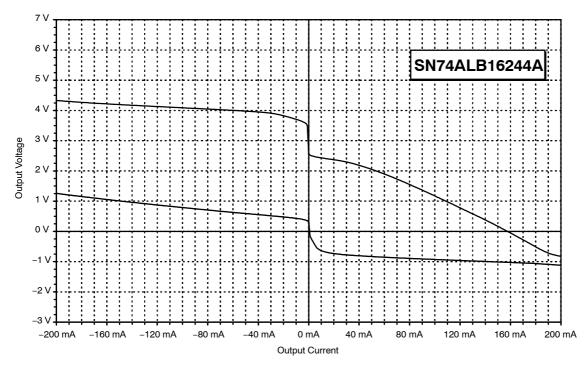

| Output Characteristics of the SN74ALB16244A        | 1–74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

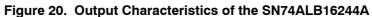

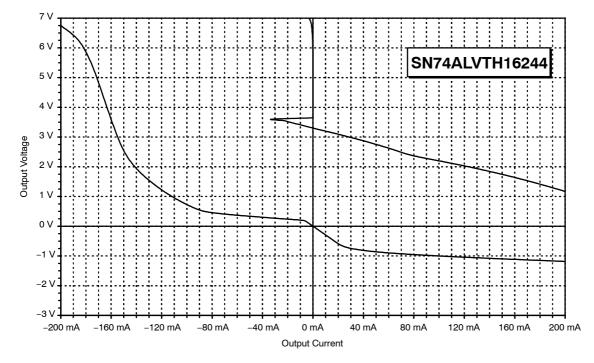

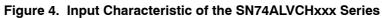

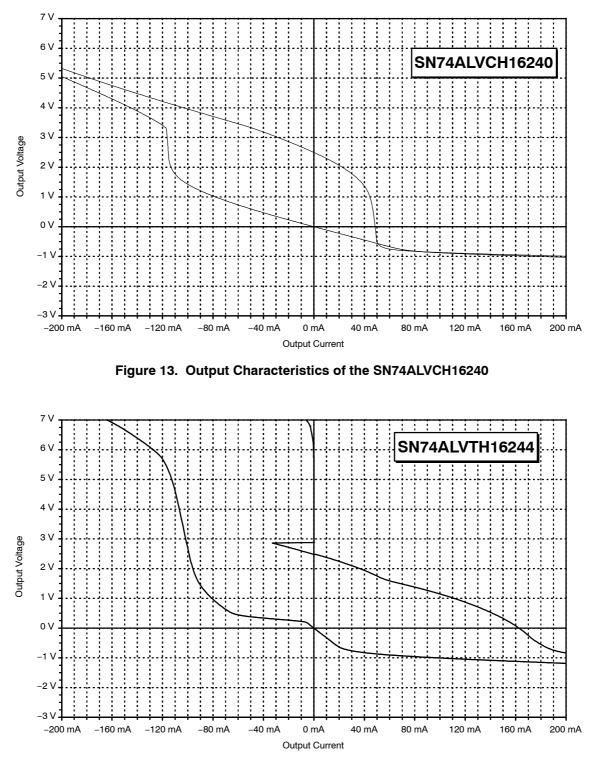

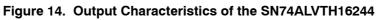

| Output Characteristics of the SN74ALVTH16244       | 1–74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Measurement Setup for the Bergeron Method          | 1–75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bergeron Diagram for the SN74ALVTH16244            | 1–76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Diagram of Line Reflections for the SN74ALVTH16244 | 1–77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Signal Shape of the SN74ALVTH16244                 | 1–78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output Waveforms of the SN74AHC240                 | 1–79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output Waveforms of the SN74AC240                  | 1-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output Waveforms of the SN74LV00A                  | 1-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output Waveforms of the SN74LV240A                 | 1–81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output Waveforms of the SN74LVC244A                | 1–81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

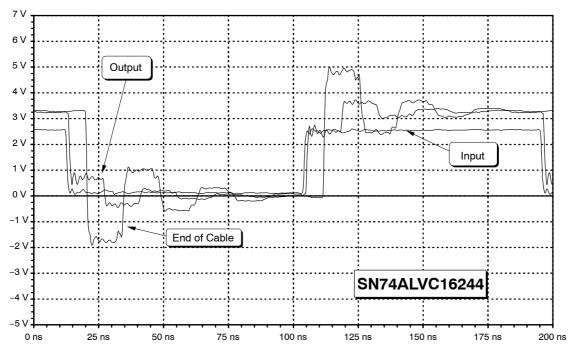

| Output Waveforms of the SN74ALVC16244              | 1-82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

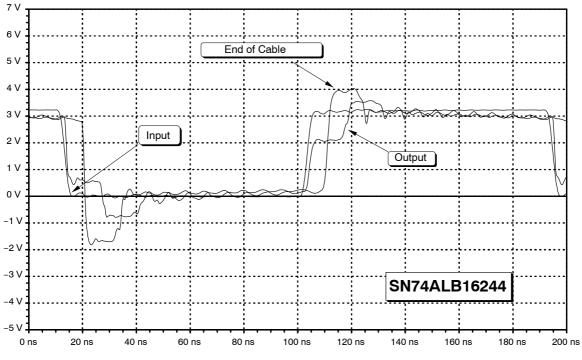

| Output Waveforms of the SN74ALB16244               | 1-82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

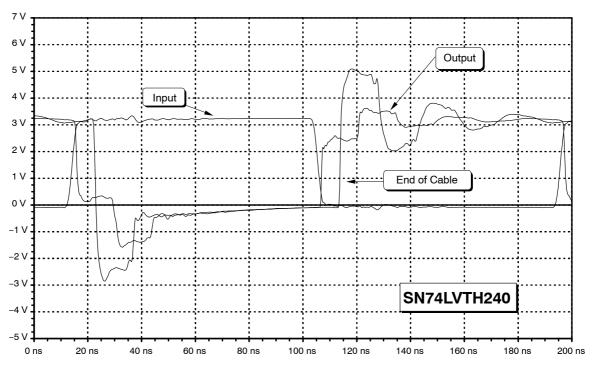

| Output Waveforms of the SN74LVTH240                | 1-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

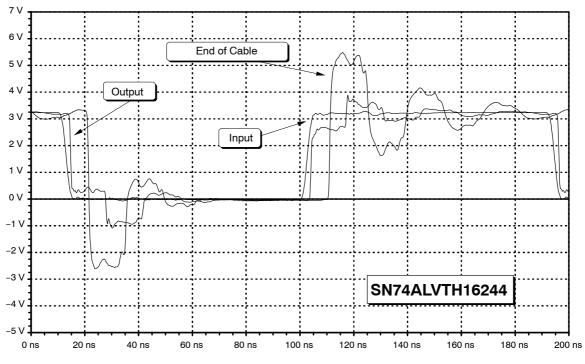

| Output Waveforms of the SN74ALVTH16244             | 1-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    | TitleOutput Characteristics of the SN74LVC00AOutput Characteristics of the SN74LVC240AOutput Characteristics of the SN74ALVCH16240Output Characteristics of the SN74ALVTH240Output Characteristics of the SN74LVTH240Output Characteristics of the SN74ALVTH16244Output Characteristics of the SN74ALVTH16244Measurement Setup for the Bergeron MethodBergeron Diagram for the SN74ALVTH16244Diagram of Line Reflections for the SN74ALVTH16244Signal Shape of the SN74ALVTH16244Output Waveforms of the SN74ALC240Output Waveforms of the SN74LV240AOutput Waveforms of the SN74LV240AOutput Waveforms of the SN74LVC16244Output Waveforms of the SN74ALVC16244Output Waveforms of the SN74ALVTH240Output Waveforms of the SN74ALVTH16244 |

## Abstract

This application report contains a comprehensive collection of the input- and output-characteristic curves of integrated circuits from various 3.3-V logic families. These curves go beyond the information given in data sheets by providing additional details regarding the characteristics of the components. This knowledge is particularly useful when, for example, a decision must be made as to which circuit should be used in a bus system, or when the waveforms that can be expected in a transmission system must be predicted using a Bergeron chart. These oscillograms are of great assistance when generating models for simulation programs that analyze the dynamic behavior of the integrated circuits in a particular environment.

## 1 Introduction

The parameters given in the data sheets of integrated circuits can give only a very limited indication of their behavior in a system. Generally, data sheets give only information regarding the behavior over the input and output (I/O) voltage range of 0 to 3.3 V. Even the output currents specified over this range provide an incomplete picture of in-system performance.

Behavior of integrated circuits outside the usually accepted operating conditions often is of interest. This is, for example, the situation when the characteristic curves need to be used to predict the signal waveforms resulting from line reflections.

Along with the I/O characteristics, use of the Bergeron method, and knowledge of the load resistor, the amplitude of the line reflections can be determined.

Many modern logic families are specified at different voltage nodes, for example the AHC logic, and can be used at 5-V, 3.3-V, or even at 2.5-V supply voltage.

Since three main voltage nodes currently are used, it is necessary to provide I/O-characteristics at these different voltage levels. This report deals exclusively with devices operated at 3.3-V supply voltage.

Two other application reports regarding this topic are available:

- Input and Output Characteristics of Digital Integrated Circuits at 5-V Supply Voltage, literature number SZZA008

- Input and Output Characteristics of Digital Integrated Circuits at 2.5-V Supply Voltage, literature number SZZA012

In view of the wide range of integrated circuits that are available, it has been necessary to limit this information to typical characteristics only. In the second and third sections of this application report, the input and output characteristics of the following circuits have been shown as being representative of other components that behave similarly in circuit:

- <sup>'00</sup> The characteristic curves of this NAND gate are given as representative of all logic circuits having normal drive capability, such as gates, flip-flops, counters, multiplexers, etc.

- <sup>2</sup>240/<sup>2</sup>244 The output characteristics of these bus-interface circuits are of particular importance when a decision must be made as to which circuit family should be used for a specific system requirement. The available output current has a decisive influence on the distortion of signals on bus lines.

- '16240/'16244 The output characteristics of these bus-interface devices correspond with the '240/'244 functions regarding the electrical behavior. However, these devices support 16 drivers within one package. This meets the market requirements, because modern designs are based on wider buses, using 16 bits, 32 bits, or more bits on the backplanes. Further, the noise behavior of the Widebus<sup>™</sup> shows a significant improvement versus the standard octal packages.

Representatives of the different logic families (see Table 1) give an overview of the input and output characteristics, which are presented in sections 2 and 3.

| FAMILY   | ТҮРЕ         |              |              |

|----------|--------------|--------------|--------------|

|          | '00          | '240/'244    | '16244       |

| SN74AHC  | $\checkmark$ | $\checkmark$ |              |

| SN74AC   | $\checkmark$ | $\checkmark$ |              |

| SN74LV   | $\checkmark$ | $\checkmark$ |              |

| SN74LVC  |              | $\checkmark$ |              |

| SN74ALVC |              |              | $\checkmark$ |

| SN74ALB  |              |              | $\checkmark$ |

| SN74ALVT |              |              | $\checkmark$ |

| SN74LVT  |              | $\checkmark$ |              |

Table 1. Representatives of the Different Logic Families

Because the input characteristics depend exclusively on the technology used, not on the logical function of the device, only one representative per logic family is shown (gate function '00 or driver function '240) in the input-characteristics section.

Section 4 of this application report presents the calculation of line reflections using the Bergeron method. The calculation is done with the SN74ALVTH16244.

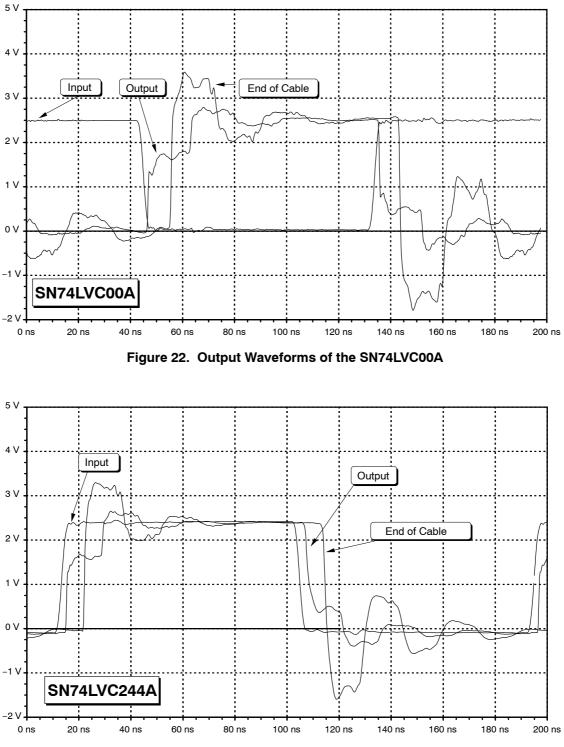

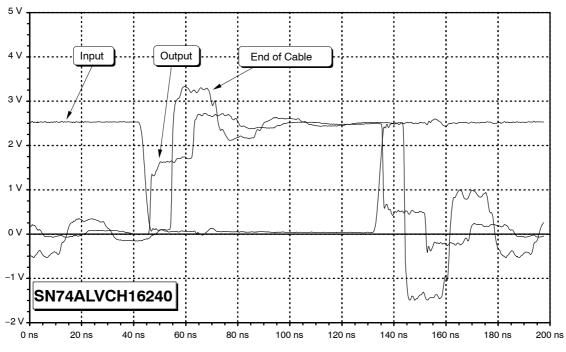

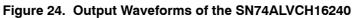

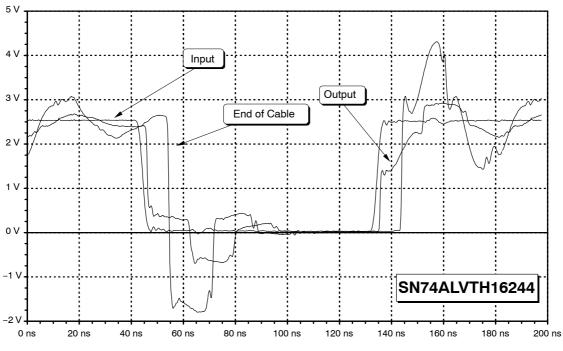

Measurement results demonstrating different switching behaviors of the various logic families are given in Section 5. For these measurements, the devices under test were loaded with a 1.3-m-long coaxial cable having a characteristic impedance of 50  $\Omega$ ; the end of the line was not connected, i.e., open circuit. These waveforms provide good insight into the dynamic behavior of the devices.

## 2 Input Characteristics

The high impedance of the input stage of the logic circuit determines the input characteristics of logic circuits in the positive range.

In contrast to the 5-V logic families, all of the 3.3-V families have CMOS input stages. The technologies used are based on the CMOS or the BiCMOS manufacturing process. In both cases, CMOS input stages are used. CMOS input stages are controlled exclusively by the applied voltage, so there is no current flowing into the input stage. Therefore, the input impedance of CMOS and BiCMOS devices is in the megaohm range. Negative voltage peaks are limited by a protection diode.

The input stages of some CMOS and BiCMOS logic families (SN74AC, SN74ALB) also have an input protection diode connected to  $V_{CC}$ . This diode limits the positive input voltage to maximum  $V_{CC}$ + 0.7 V, but prohibits their use in mixed-voltage systems.

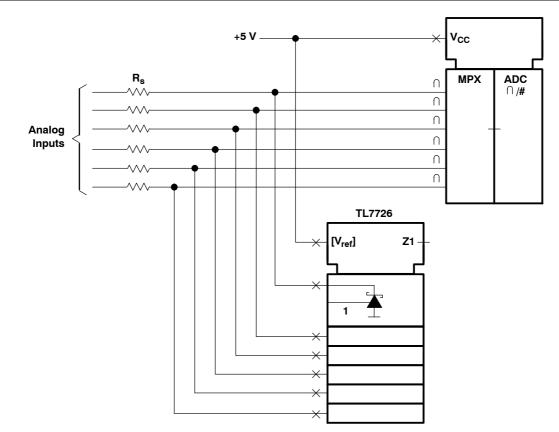

The bus-hold circuit represents a special input circuit that is implemented in the input stages of the LVT and ALVT logic families and is optionally available for the LVC and ALVC family devices.

Inputs of components that have the bus-hold circuit hold the last valid logic state. This feature is suitable in the case where an input stays undefined, e.g., during a high-impedance state on the bus. Using the bus-hold circuit eliminates the need for pullup or pulldown resistors.

Devices with the bus-hold circuit are designated by the 'H' in their part numbers, for example, SN74LVTH245.

A more detailed application report, *Bus-Hold Circuits*, literature number SDZAE15, is available from Texas Instruments (TI™).

A list of application reports and other literature is given in Section 7.

Figure 1. Input Characteristic of the SN74AHCxxx Series

Figure 5. Input Characteristic of the SN74ALVCxxx Series

Figure 7. Input Characteristic of the SN74LVTHxxx Series

Figure 8. Input Characteristic of the SN74ALVTHxxx Series

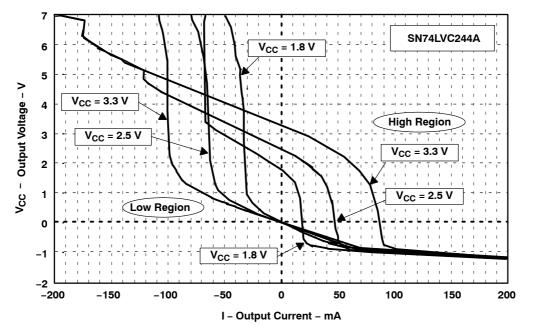

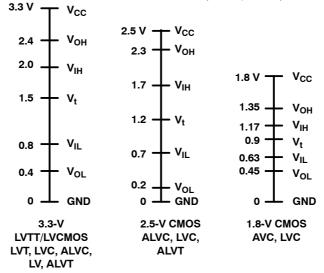

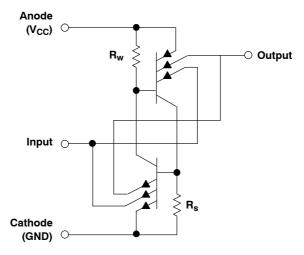

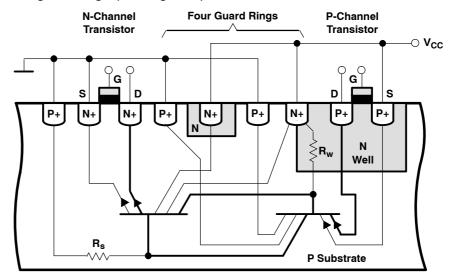

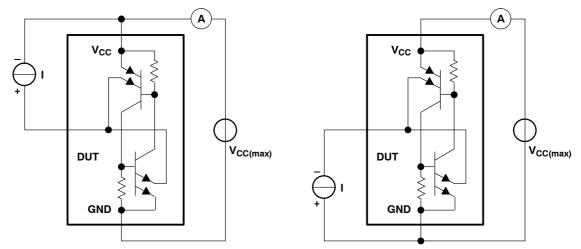

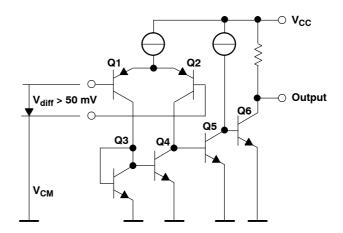

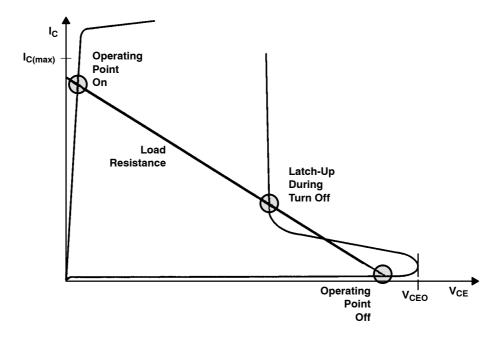

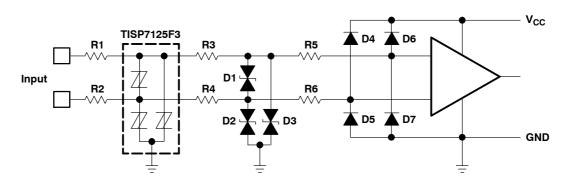

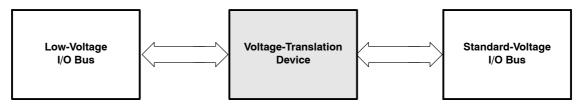

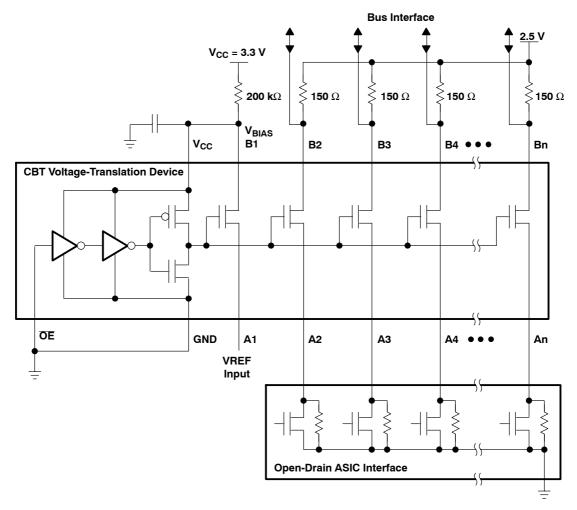

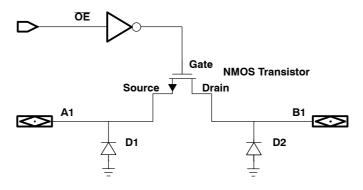

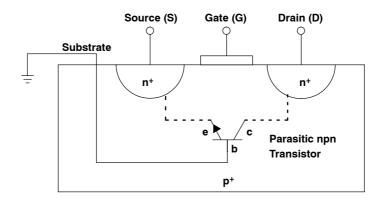

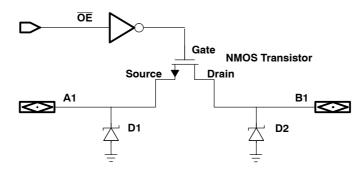

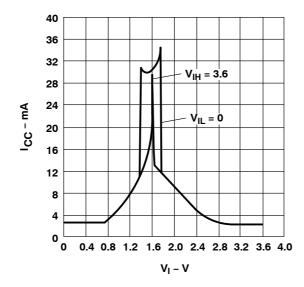

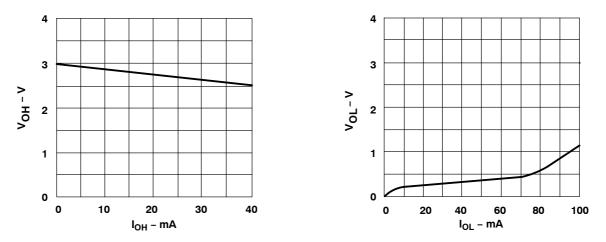

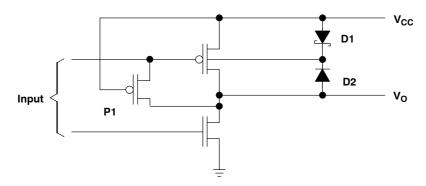

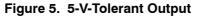

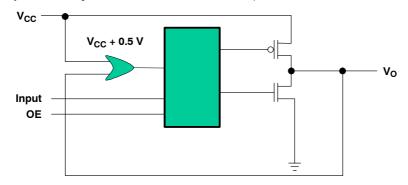

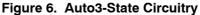

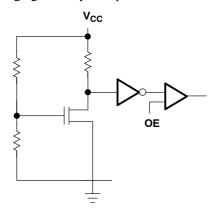

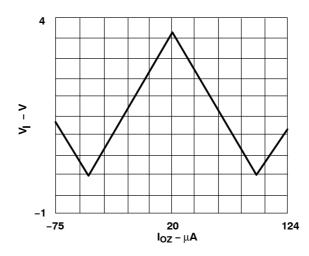

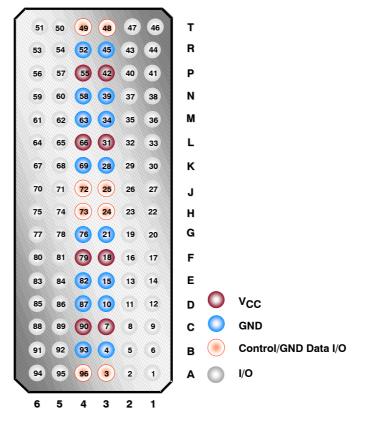

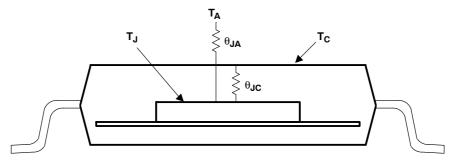

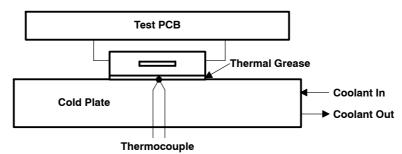

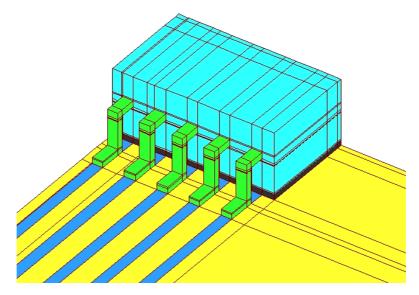

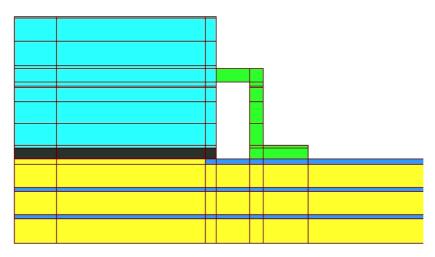

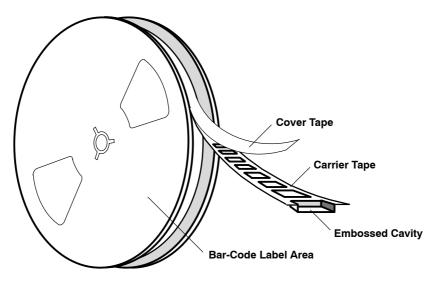

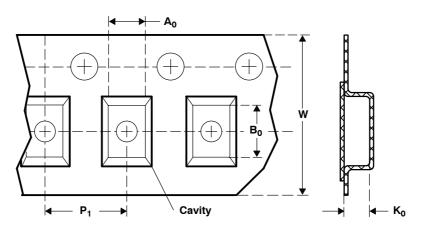

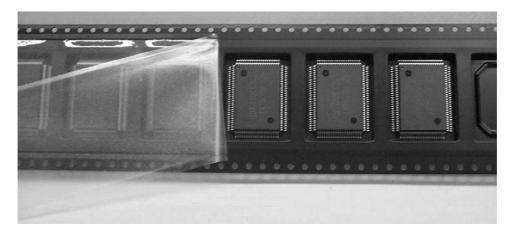

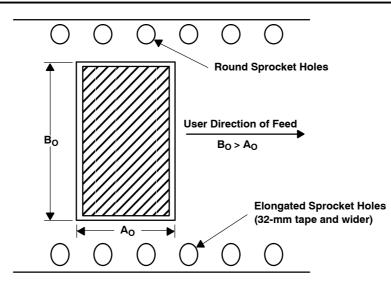

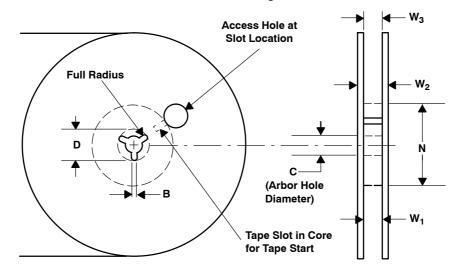

## **3 Output Characteristics**