# **Design Considerations for Logic Products**

Volume 2

September 1999

Logic Products

SDYA018

September 1999

Design Considerations for Logic Products

Ų

## **Design Considerations for Logic Products**

September 1999

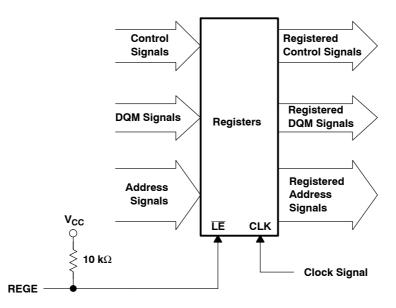

Logic Products

SDYA018

Ų

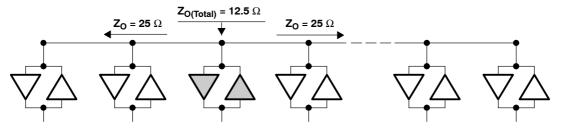

September 1999

Application Book Volume 2

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| ABT Advanced BiCMOS Technology Characterization Information |   |

|-------------------------------------------------------------|---|

| Advanced High-Speed CMOS (AHC) Logic Family 1–6             | 1 |

| AHC/AHCT Designer's Guide 1–8                               | 3 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| LVT Family Characteristics | . 2–3  |

|----------------------------|--------|

| LVT-to-LVTH Conversion     | . 2–21 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| AVC Logic Family Technology and Applications     |                      |

|--------------------------------------------------|----------------------|

| Migration From 3.3-V to 2.5-V Power Supplies for | r Logic Devices 3-29 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| Page                                                                                                 |

|------------------------------------------------------------------------------------------------------|

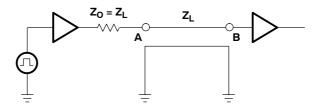

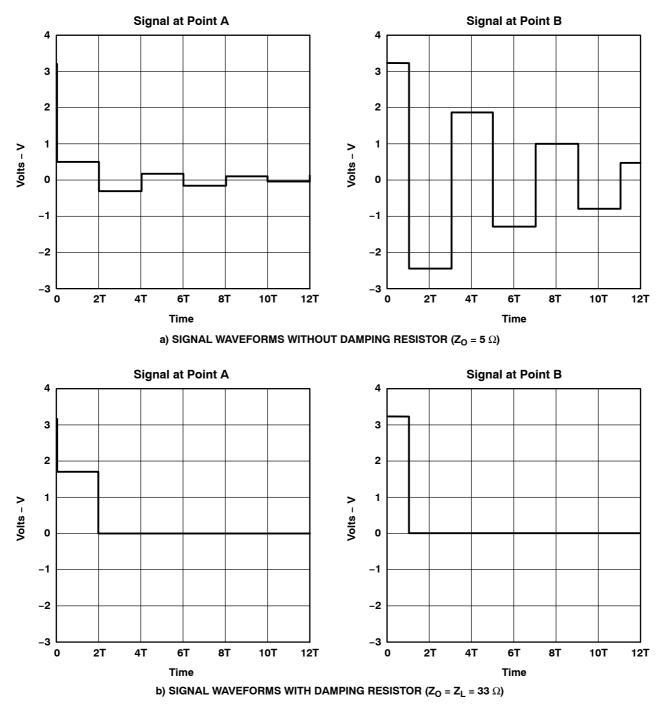

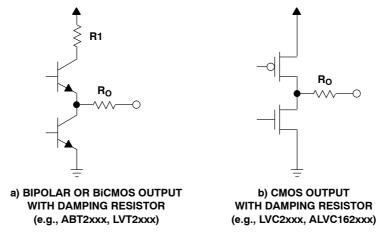

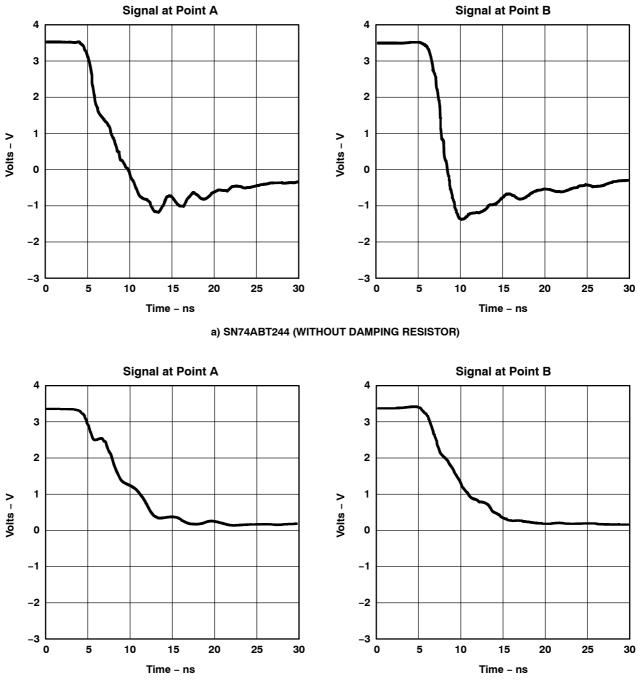

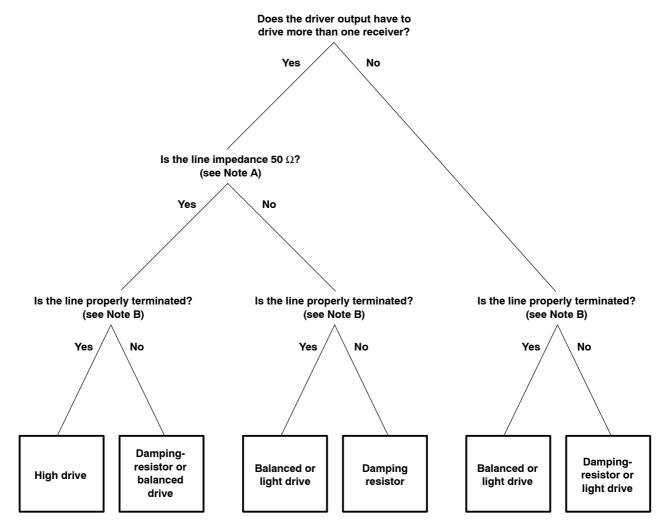

| Bus-Interface Devices With Output-Damping Resistors or Reduced-Drive Outputs 4–3                     |

| CMOS Power Consumption and C <sub>PD</sub> Calculation                                               |

| Dynamic Output Control (DOC™) Circuitry Technology and Applications                                  |

| Implications of Slow or Floating CMOS Inputs                                                         |

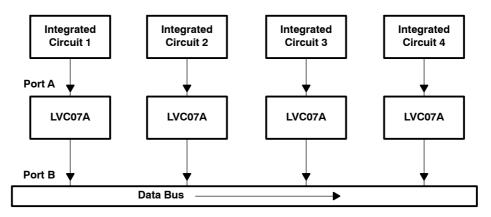

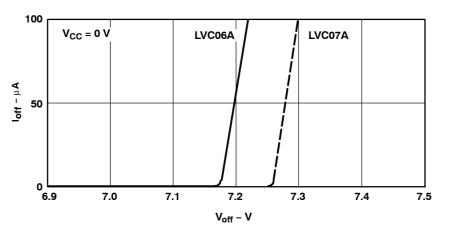

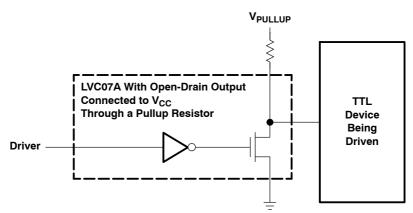

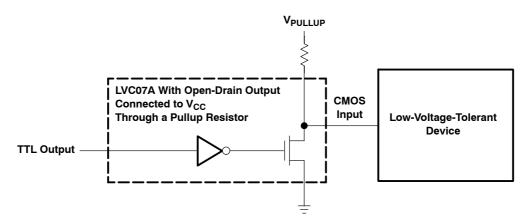

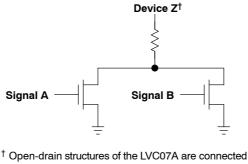

| LVC07A: Applications of an Open-Drain Hex Buffer                                                     |

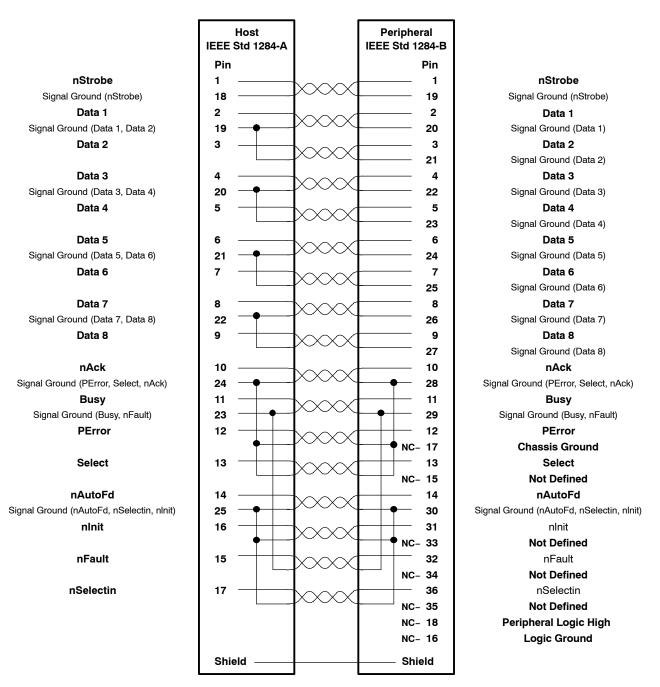

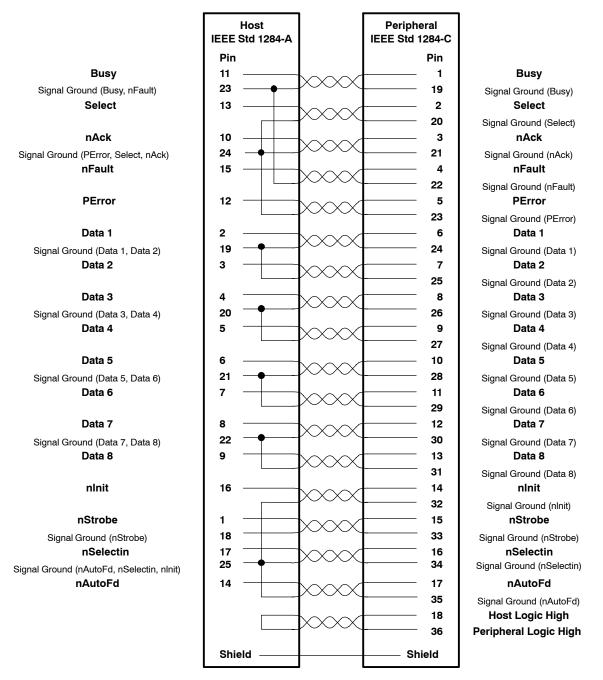

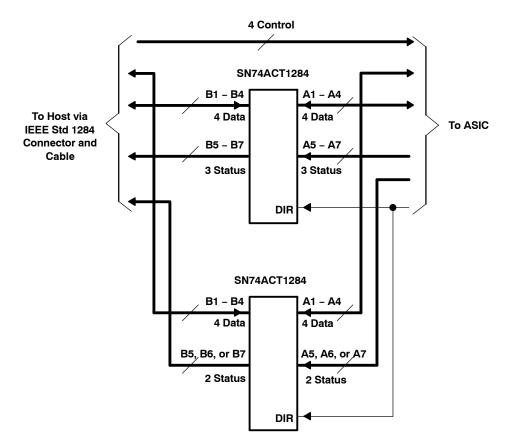

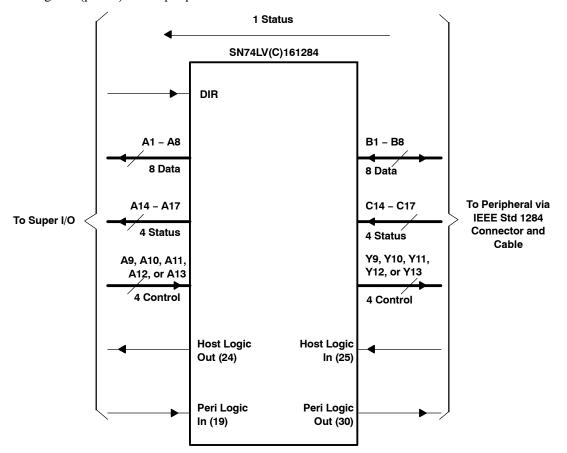

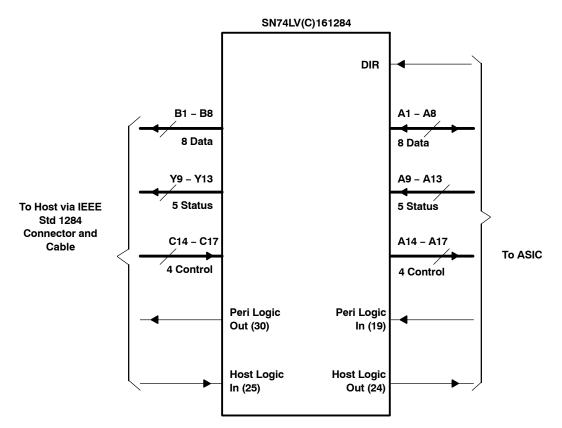

| Logic Solutions for IEEE Std 1284                                                                    |

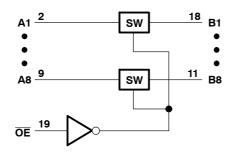

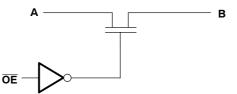

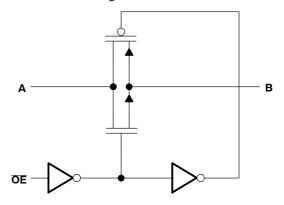

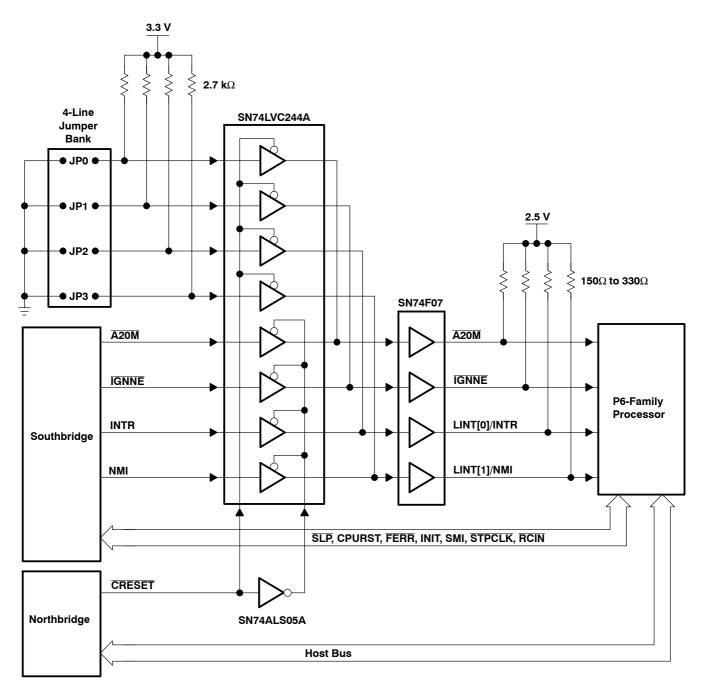

| Low-Voltage Bus-Switch Technology and Applications                                                   |

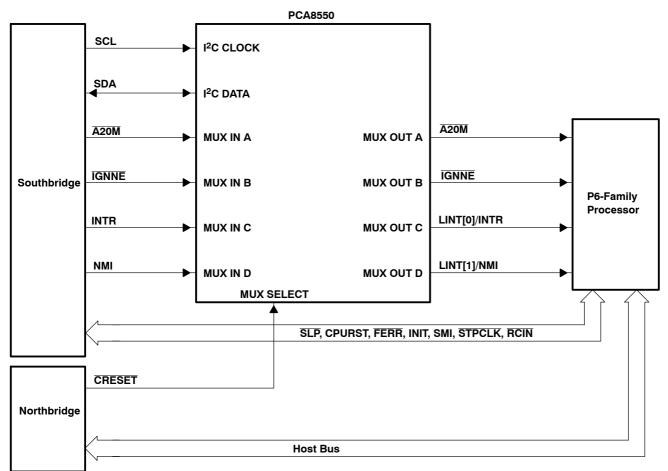

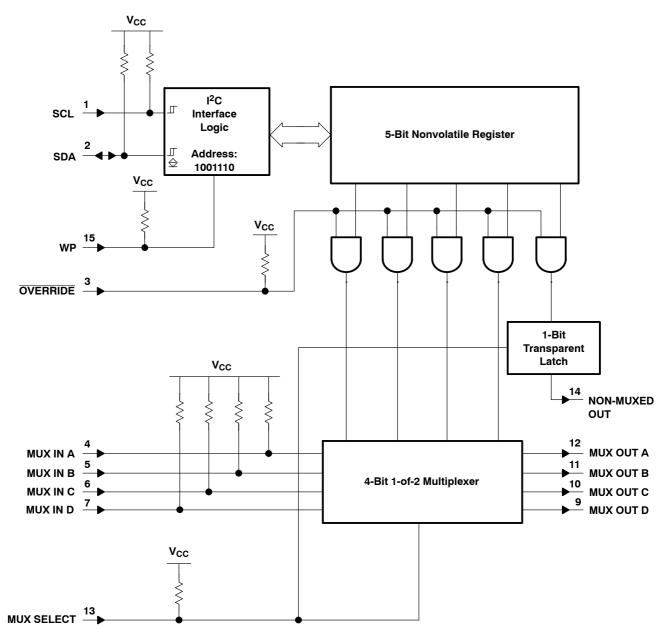

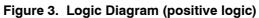

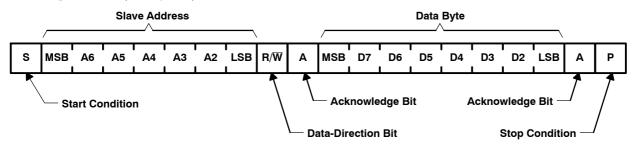

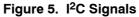

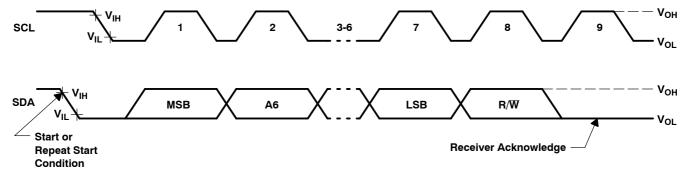

| PCA8550 Nonvolatile 5-Bit Register with I <sup>2</sup> C Interface Technology and Applications 4–123 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| Logic Solutions for PC100 SDRAM Registered DIMMs                         | 5–3  |

|--------------------------------------------------------------------------|------|

| SSTL for DIMM Applications                                               | 5–25 |

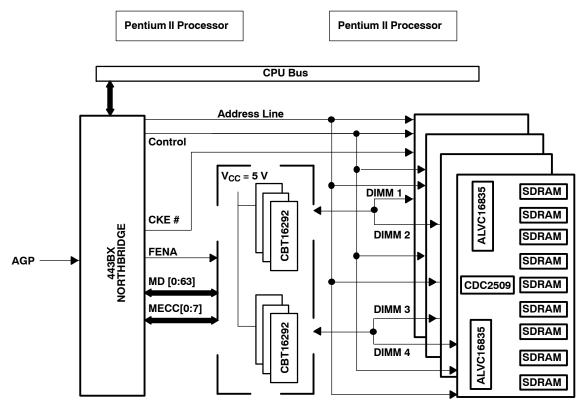

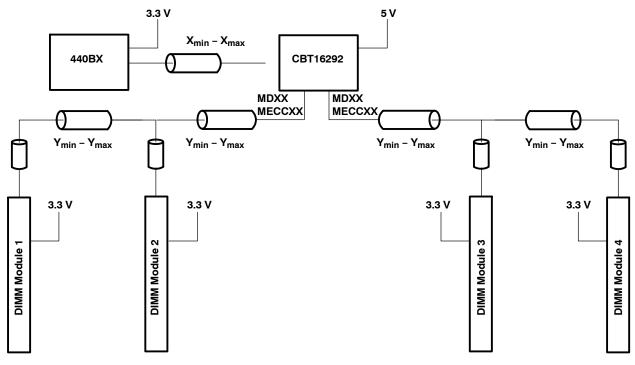

| TI Logic Solutions for Memory Interleaving With the Intel™ 440BX Chipset | 5–35 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

| Basic Design Considerations for Backplanes  | 6–3  |

|---------------------------------------------|------|

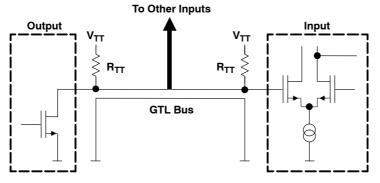

| Fast GTL Backplanes With the GTL1655        | 6–19 |

| High-Performance Backplane Design With GTL+ | 6–61 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

|                                                                                                 | Page    |

|-------------------------------------------------------------------------------------------------|---------|

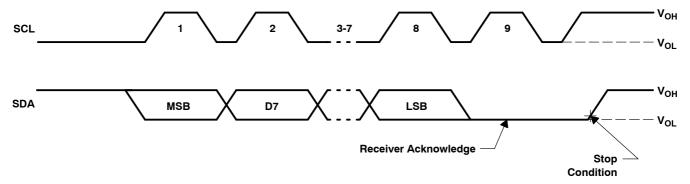

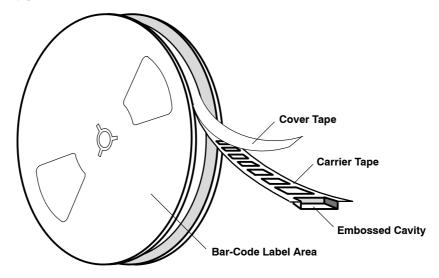

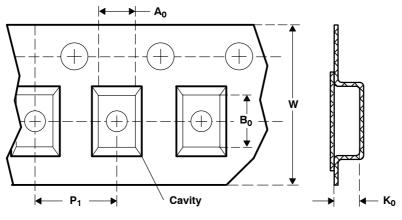

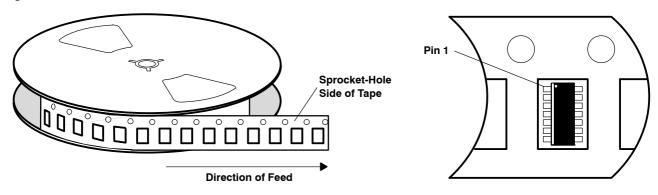

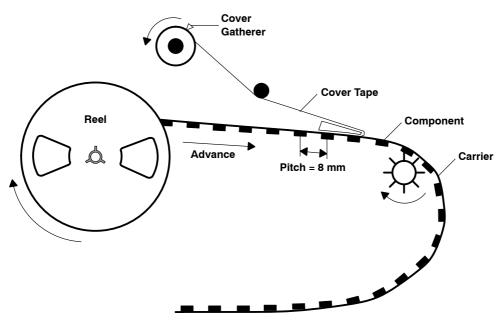

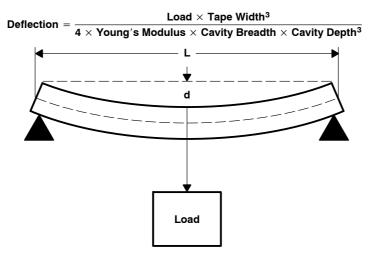

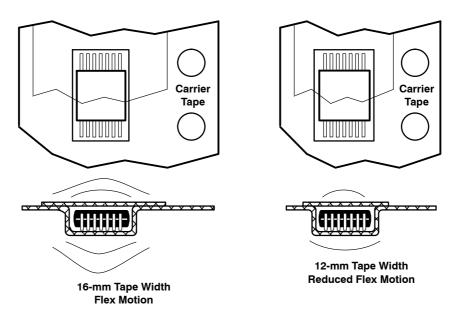

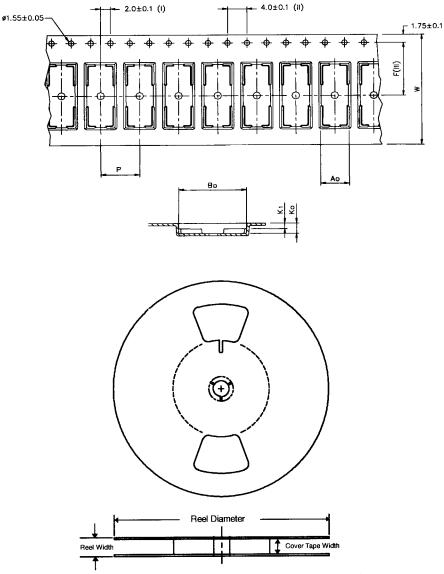

| 12-mm Tape-and-Reel Component-Delivery System                                                   | . 7–3   |

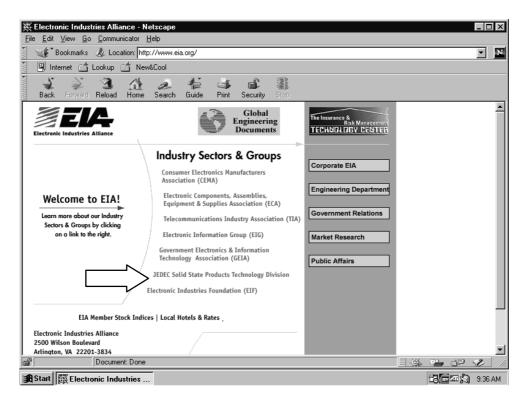

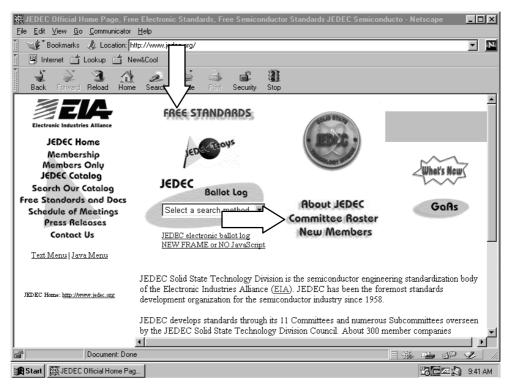

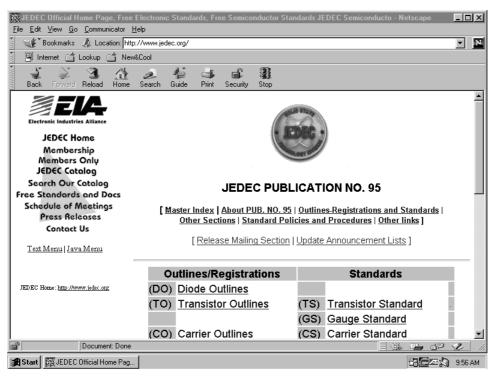

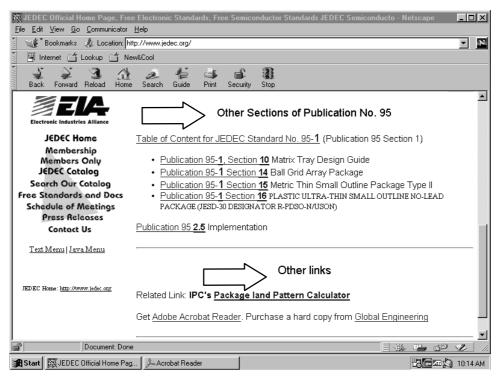

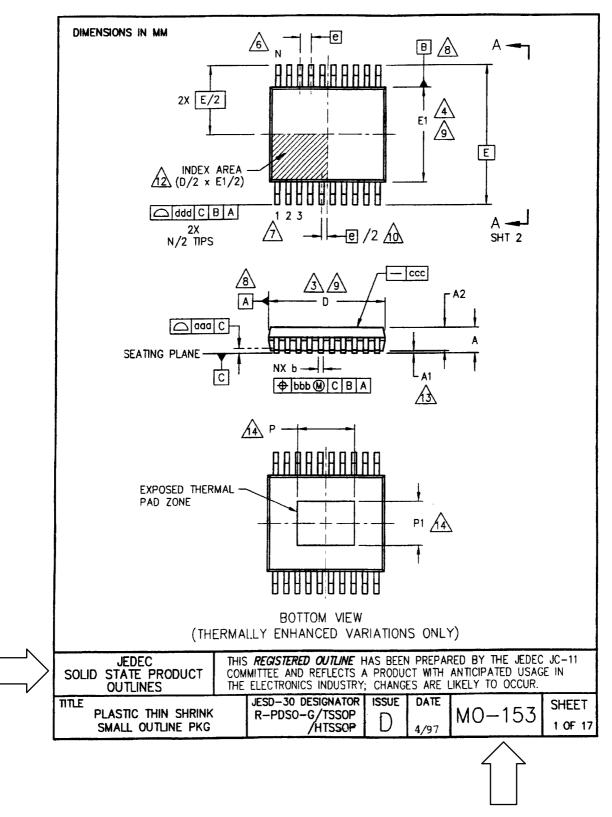

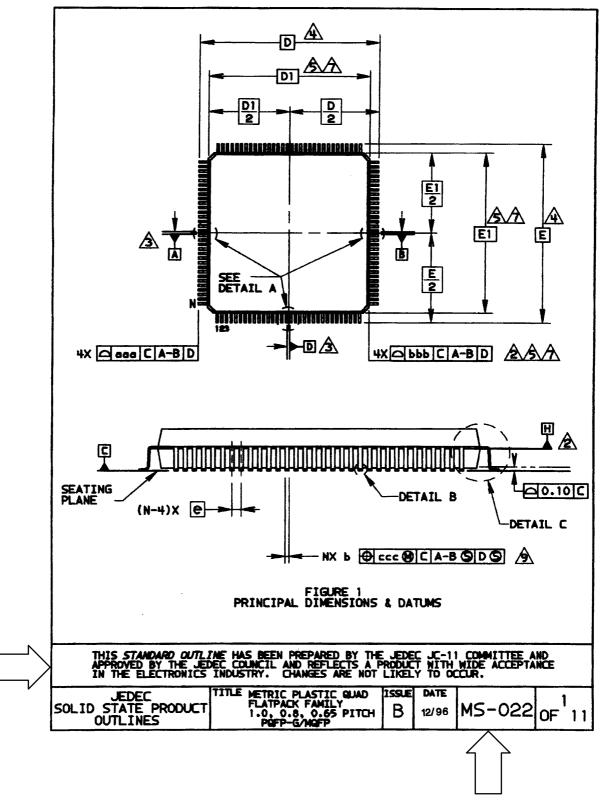

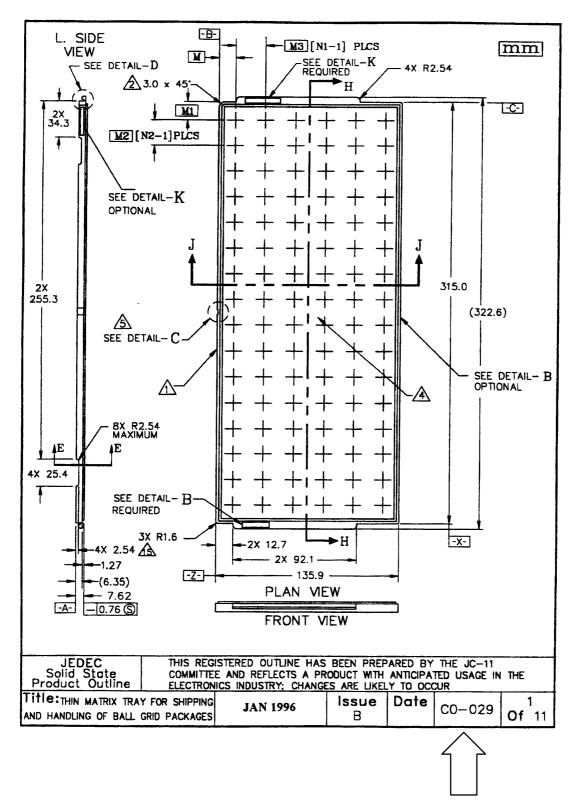

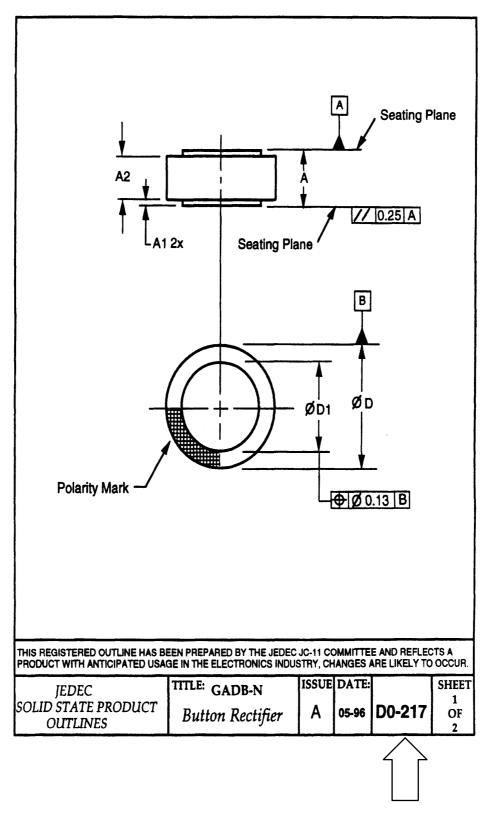

| JEDEC Publication 95 Microelectronic Package Standard                                           | . 7–15  |

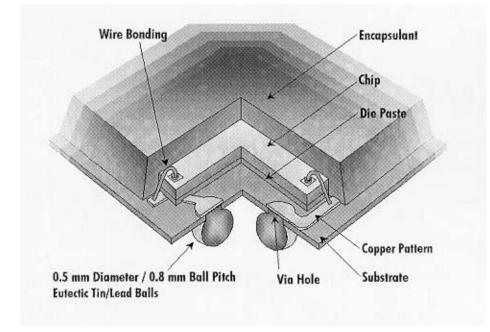

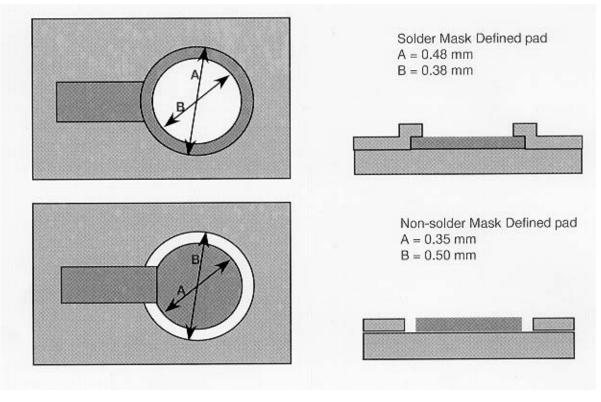

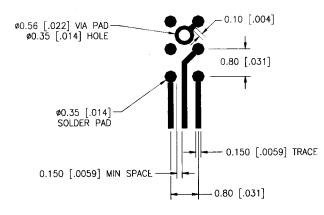

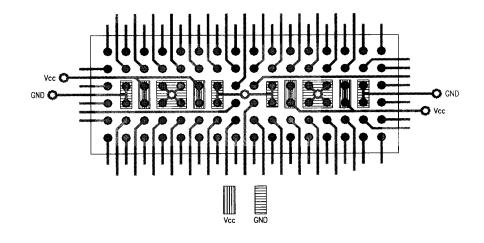

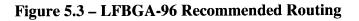

| 32-Bit Logic Families in LFBGA Packages: 96 and 114 Ball Low-Profile<br>Fine-Pitch BGA Packages | . 7–37  |

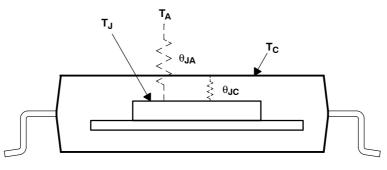

| Package Thermal Characterization Methodologies                                                  | . 7–65  |

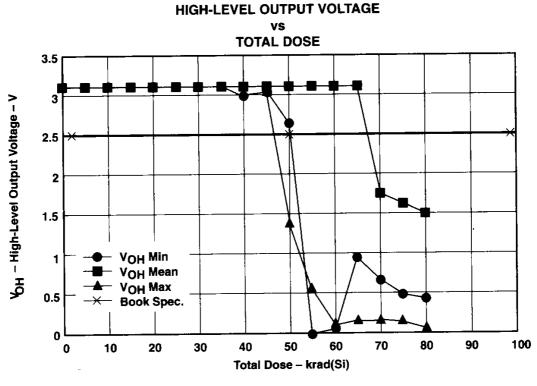

| Radiation Exposure Test Results of F Logic Functions                                            | . 7–79  |

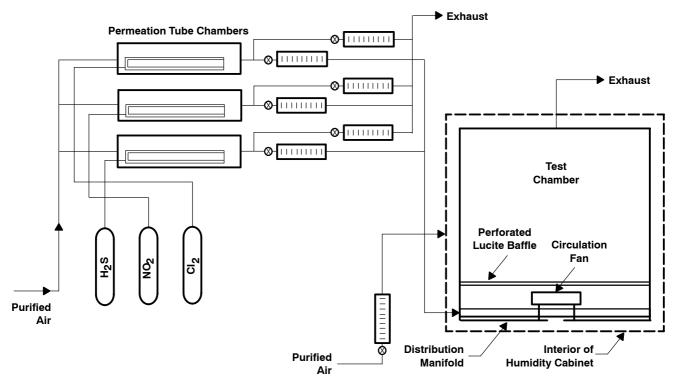

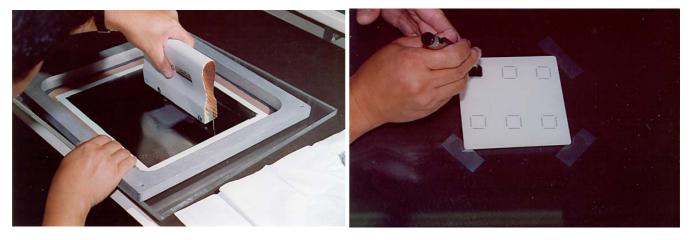

| Shelf-Life Evaluation of Nickel/Palladium Lead Finish for Integrated Circuits                   | . 7–91  |

| Steam-Age Evaluation of Nickel/Palladium Lead Finish for Integrated Circuits                    | . 7–103 |

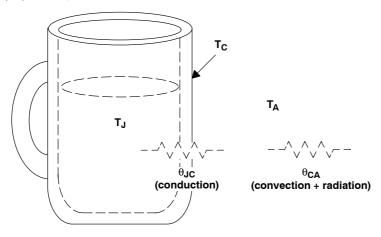

| Thermal Characteristics of Standard Linear and Logic (SLL) Packages and Devices $\ldots$        | . 7–117 |

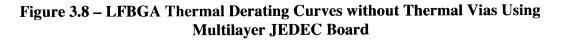

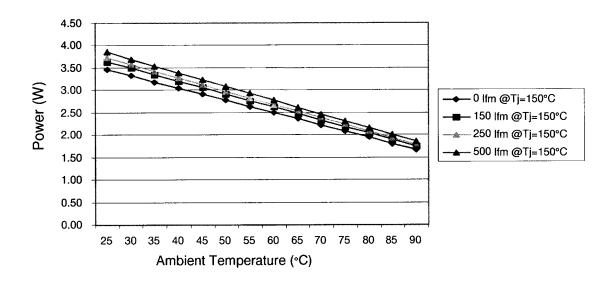

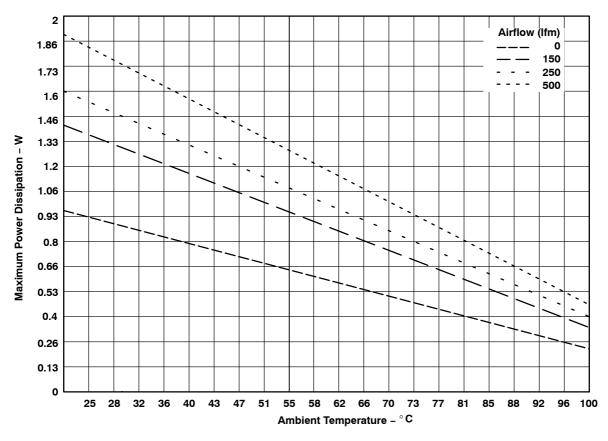

| Thermal Derating Curves for Logic-Products Packages                                             | . 7–135 |

| 5-V Logic Design               | 1 |

|--------------------------------|---|

| 3.3-V Logic Design             | 2 |

| 2.5-V Logic Design             | 3 |

| Device-Specific Design Aspects | 4 |

| DIMM Applications              | 5 |

| Backplane Applications         | 6 |

| Packaging                      | 7 |

| Appendix A                     | Α |

## Design Considerations for Logic Products Application Book

Volume 2

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

#### INTRODUCTION

This collection of application reports and articles provides the design engineer with a valuable technical reference for Texas Instruments (TI<sup>™</sup>) products. It contains reports written or revised between March 1997 and July 1999. This book is divided into seven sections, each focusing on different aspects of design decisions, and an appendix listing application reports published in the 1997 *Design Considerations for Logic Products* Application Book, literature number SDYA002.

Section 1, *5-V Logic Design*, includes discussions on the ABT (Advanced BiCMOS Technology) and AHC (Advanced High-Speed CMOS) logic families. ABT and AHC devices are the recommended families for medium- to high-performance 5-V designs.

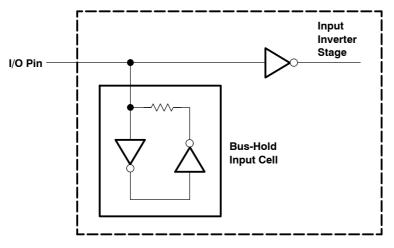

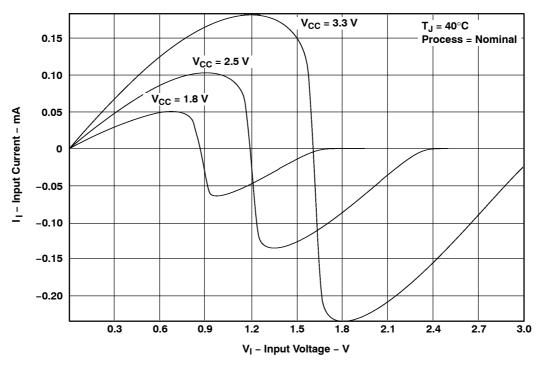

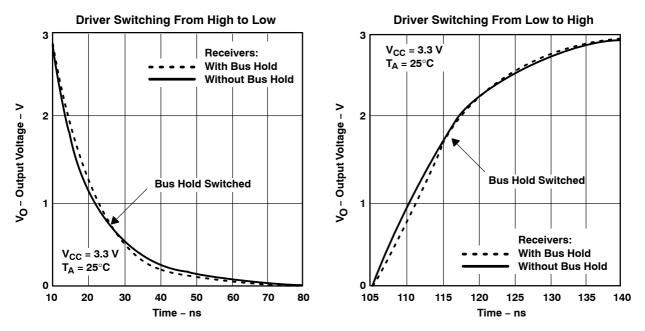

Section 2, **3.3-V Logic Design**, focuses on the LVT (Low-Voltage BiCMOS Technology) logic family. The LVT family has performance specifications ideal for networking and telecommunication applications. This section includes application reports explaining the LVT-to-LVTH conversion. When using the new LVT or LVTH devices in existing applications, some customers may need to deal with timing of the marginally faster devices, or they may have used resistors at the input to the bus-hold circuitry that would need to be resized because of a change in the maximum bus-hold current.

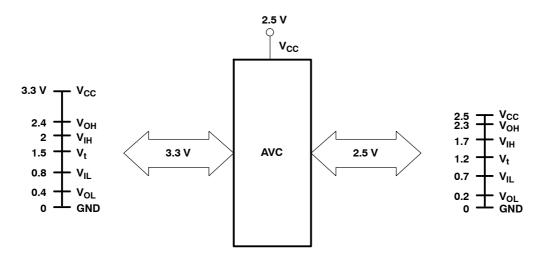

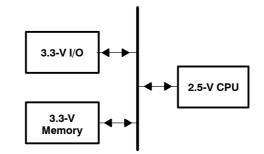

Section 3, *2.5-V Logic Design*, addresses the migration from 3.3-V to 2.5-V logic devices in current designs. Additionally, this section focuses on the use of the AVC (Advanced Very-Low-Voltage CMOS) logic family in next-generation, high-performance PCs, workstations, and servers.

Section 4, **Device-Specific Design Aspects**, covers damping resistors, dynamic output control (DOC<sup>™</sup>), I<sup>2</sup>C interface, and other device-specific characteristics and features not covered in the 1997 edition of *Design Considerations for Logic Products* application book.

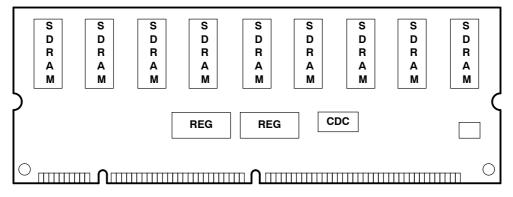

Section 5, *DIMM Applications*, explains logic buffering solutions for dual inline memory modules (DIMM) using ALVC (Advanced Low-Voltage CMOS) and SSTL (Stub Series-Terminated Logic) and memory interleaving using for the 440BX and other core-logic chipsets using CBT and CBTLV.

Section 6, *Backplane Applications*, addresses basic aspects of designing a backplane system, focusing on the GTL+ switching standard and design with the TI SN74GTL1655.

Section 7, *Packaging*, gives an overview of standard packages for logic products. From DIP to the advanced low-profile, fine-pitch ball grid array (LFBGA) package, this section covers shelf-life evaluation, steam-age evaluation, thermal characteristics, and other considerations when selecting a package for a design.

For more information on these or other TI Products, please contact your local TI representative, authorized distributor, the TI technical support hotline at 972-644-5580, or visit the TI logic home page at http://www.ti.com/sc/logic. Application reports published in the previous *Design Considerations for Logic Products* Application Book (see appendix A) also are available through links on the TI logic home page.

DOC and TI are trademarks of Texas Instruments Incorporated.

| 1 | 5-V Logic Design 1-                                                                            |

|---|------------------------------------------------------------------------------------------------|

|   | ABT Advanced BiCMOS Technology Characterization Information                                    |

|   | Advanced High-Speed CMOS (AHC) Logic Family 1-6                                                |

|   | AHC/AHCT Designer's Guide 1-8                                                                  |

| 2 | 3.3-V Logic Design 2-                                                                          |

|   | LVT Family Characteristics                                                                     |

|   | LVT-to-LVTH Conversion                                                                         |

| 3 | 2.5-V Logic Design 3-                                                                          |

|   | AVC Logic Family Technology and Applications                                                   |

|   | Migration From 3.3-V to 2.5-V Power Supplies for Logic Devices                                 |

| 4 | Device-Specific Design Aspects 4-                                                              |

|   | Bus-Interface Devices With Output-Damping Resistors or Reduced-Drive Outputs                   |

|   | CMOS Power Consumption and C <sub>pd</sub> Calculation                                         |

|   | Dynamic Output Control (DOC™) Circuitry Technology and Applications                            |

|   | Implications of Slow or Floating CMOS Inputs 4-6                                               |

|   | LVC07A: Applications of an Open-Drain Hex Buffer                                               |

|   | Logic Solutions for IEEE Std 1284 4-9                                                          |

|   | Low-Voltage Bus-Switch Technology and Applications                                             |

|   | PCA8550 Nonvolatile 5-Bit Register With I <sup>2</sup> C Interface Technology and Applications |

| 5 | DIMM Applications 5-                                                                           |

|   | Logic Solutions for PC100 SDRAM Registered DIMMs5-                                             |

|   | SSTL for DIMM Applications                                                                     |

|   | TI Solutions for Memory Interleaving With the Intel™ 440BX Chipset                             |

| 6 | Backplane Applications 6-                                                                      |

|   | Basic Design Considerations for Backplanes6-                                                   |

|   | Fast GTL Backplanes With the GTL1655                                                           |

|   | High-Performance Backplane Design With GTL+                                                    |

## **Contents (Continued)**

| 7 | Packaging 7–1                                                                                     |

|---|---------------------------------------------------------------------------------------------------|

|   | 12-mm Tape-and-Reel Component-Delivery System                                                     |

|   | JEDEC Publication 95 Microelectronic Package Standard                                             |

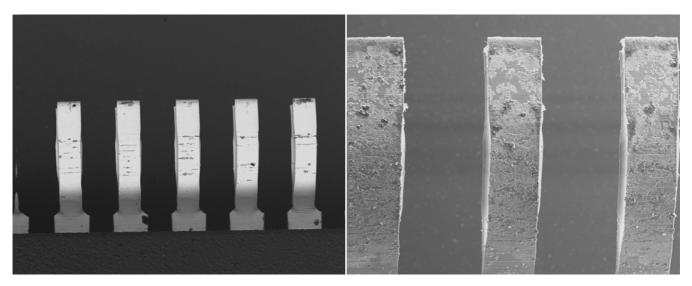

|   | 32-Bit Logic Families in LFBGA Packages: 96 and 114 Ball Low-Profile Fine-Pitch BGA Packages 7–37 |

|   | Package Thermal Characterization Methodologies                                                    |

|   | Radiation Exposure Test Results of F Logic Functions                                              |

|   | Shelf-Life Evaluation of Nickel/Palladium Lead Finish for Integrated Circuits                     |

|   | Steam-Age Evaluation of Nickel/Palladium Lead Finish for Integrated Circuits                      |

|   | Thermal Characteristics of Standard Linear and Logic (SLL) Packages and Devices                   |

|   | Thermal Derating Curves for Logic-Products Packages                                               |

| A | Appendix A-1                                                                                      |

|   | Appendix A                                                                                        |

# ABT Advanced BiCMOS Technology Characterization Information

SCBA008B June 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

## Contents

| Introduction                                                                          | 1–7  |

|---------------------------------------------------------------------------------------|------|

| AC Performance                                                                        | 1–7  |

| Power Considerations                                                                  | 1–12 |

| Input Characteristics                                                                 |      |

| Input Current Loading                                                                 | 1–14 |

| Supply Current Change (ΔI <sub>CC</sub> )         Proper Termination of Unused Inputs |      |

| Output Characteristics                                                                | 1–17 |

| Signal Integrity                                                                      | 1–19 |

| Advanced Packaging                                                                    | 1–23 |

# List of Illustrations

| Figure | Title                                                      | Page   |

|--------|------------------------------------------------------------|--------|

| 1      | Propagation Delay vs Operating Free-Air Temperature A to Y | 1–8    |

| 2      | Propagation Delay vs Number of Outputs Switching           | . 1–10 |

| 3      | Propagation Delay vs Capacitive Load                       | . 1–11 |

| 4      | Supply Current vs Frequency                                | . 1–12 |

| 5      | Simplified Input Stage of an ABT Circuit                   | . 1–13 |

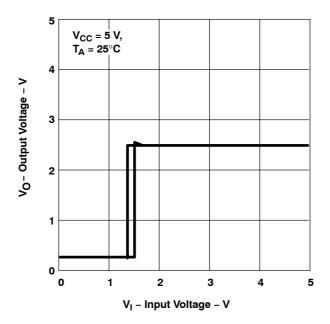

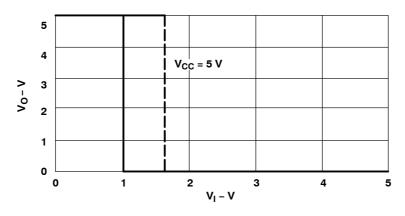

| 6      | Output Voltage vs Input Voltage                            | . 1–14 |

| 7      | Input Current vs Input Voltage                             | . 1–14 |

| 8      | Supply Current vs Input Voltage                            | . 1–15 |

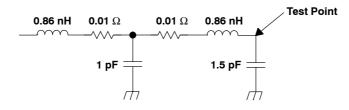

| 9      | Sample Input/Output Model                                  | . 1–16 |

| 10     | Simplified ABT Output Stage                                | . 1–17 |

| 11     | Typical ABT Output Characteristics                         | . 1–17 |

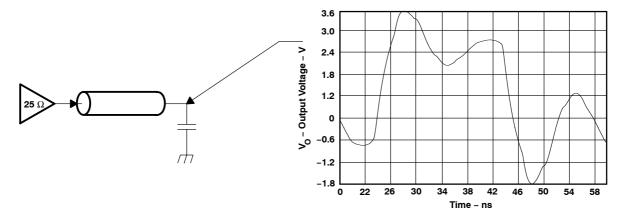

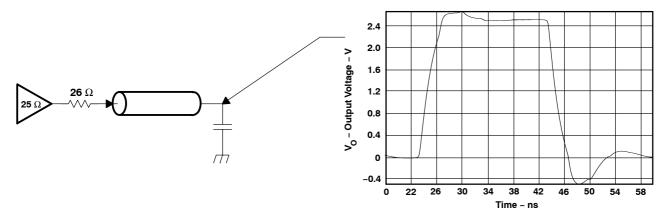

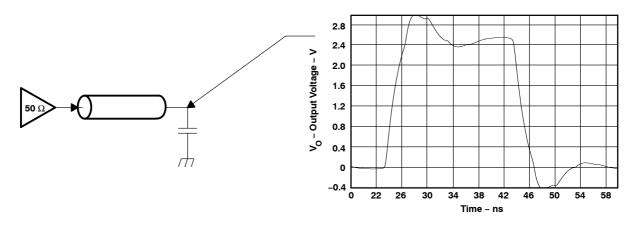

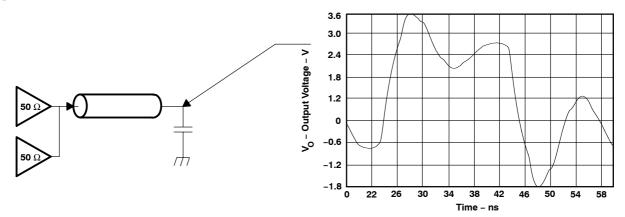

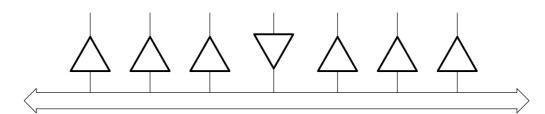

| 12     | Reflected Wave Switching                                   | . 1–18 |

| 13     | Simplified Input Structures for CMOS and ABT Devices       | . 1–19 |

| 14     | Example of Partial System Power Down                       | . 1–19 |

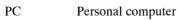

| 15     | Simultaneous-Switching Output Model                        | . 1–19 |

EPIC-IIB and Widebus are trademarks of Texas Instruments Incorporated.

Page

## List of Illustrations (continued)

| Figure | Title                                     | Page |

|--------|-------------------------------------------|------|

| 16     | Simultaneous-Switching-Noise Waveform     | 1–20 |

| 17     | TTL DC Noise Margin                       | 1–21 |

| 18     | ABT646A Simultaneous-Switching Waveform   | 1–22 |

| 19     | ABT16500B Simultaneous-Switching Waveform | 1–22 |

| 20     | 24-Pin Surface-Mount Comparison           | 1-23 |

| 21     | Distributed Pinout of 'ABT16244A          | 1–24 |

## Appendixes

Title

| Appendix A |  |

|------------|--|

| Appendix B |  |

| Appendix C |  |

#### Introduction

The purpose of this document is to assist the designers of high-performance digital logic systems in using the advanced BiCMOS technology (ABT) logic family.

Detailed electrical characteristics of these bus-interface devices are provided and tables and graphs have been included to compare specific parameters of the ABT family with those of other logic families.

In addition, typical data is provided to give the hardware designer a better understanding of how the ABT devices operate under various conditions.

The major subject areas covered in the report are as follows:

- AC Performance

- Power Considerations

- Input Characteristics

- Output Characteristics

- Signal Integrity

- Advanced Packaging

- Characterization Information

The characterization information provided is typical data and is not intended to be used as minimum or maximum specifications, unless noted as such.

For more information on these or other TI products, please contact your local TI representative, authorized distributor, the TI technical support hotline at 972-644-5580, or visit the TI logic home page at http://www.ti.com/sc/logic.

For a complete listing of all TI logic products, please order our logic CD-ROM (literature number SCBC001) or Logic Selection Guide (literature number SDYU001) by calling our literature response center at 1-800-477-8924.

#### **AC Performance**

As microprocessor operating frequencies increase, the period of time allotted for operations, such as memory access or arithmetic functions, decreases. With this in mind, TI developed a family of bus-interface devices – ABT – utilizing advanced BiCMOS technology. The goal of the ABT family of devices is to give system designers one bus-interface solution that provides high drive capability, good signal integrity, and propagation delays short enough to appear transparent with respect to overall system performance.

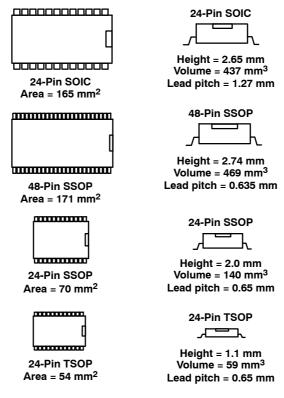

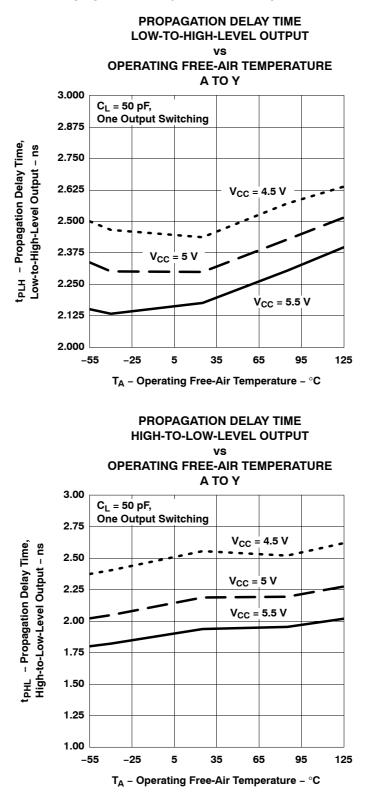

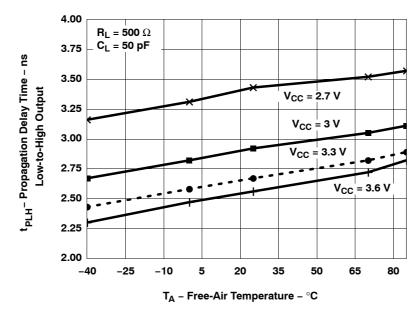

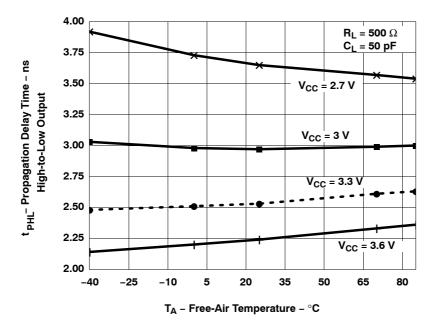

Advances in IC process technology, including smaller minimum feature size, tighter metal pitch, and shallower junctions, combine to provide stronger drive strengths and smaller parasitic capacitances. As a result, internal propagation delays have become extremely short. With the advent of the 0.8- $\mu$ m, EPIC-IIB<sup>TM</sup> BiCMOS process and new circuit innovations, the ABT family offers typical propagation delays as low as 2-3 ns as shown in Figure 1. Maximum specifications are as low as 3–5 ns, depending on the device type.

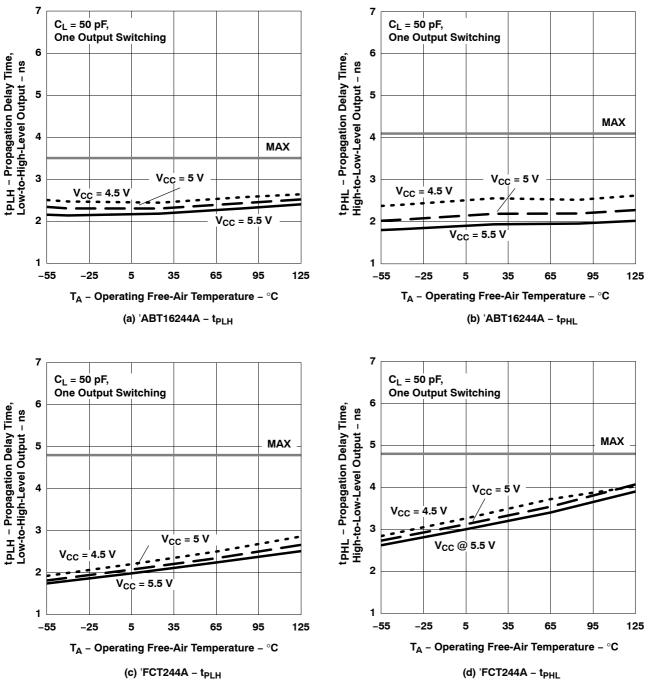

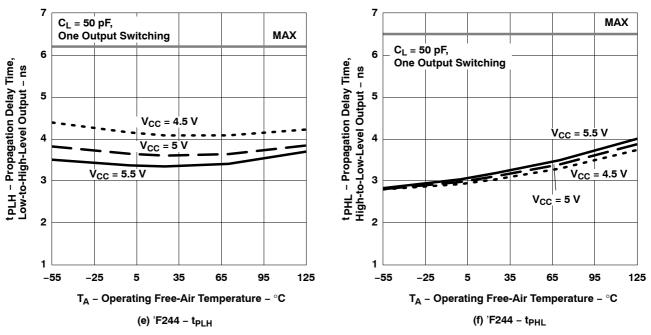

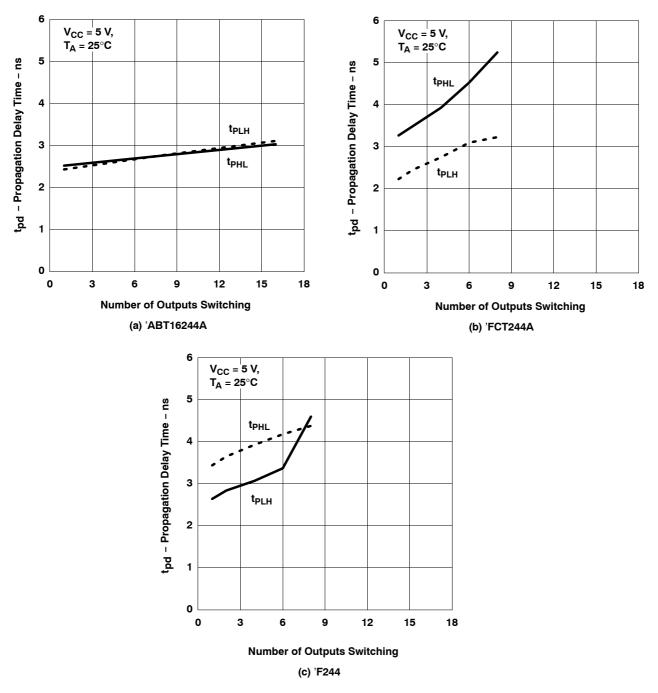

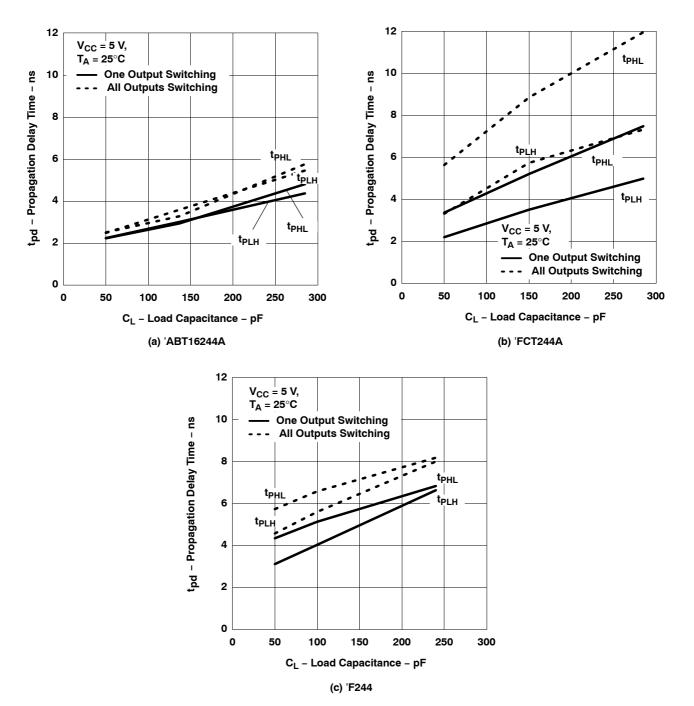

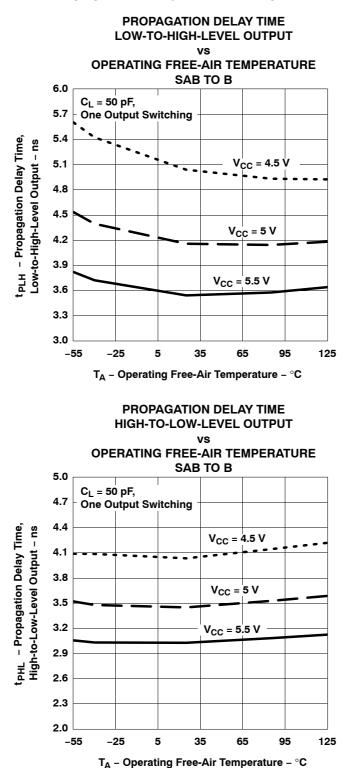

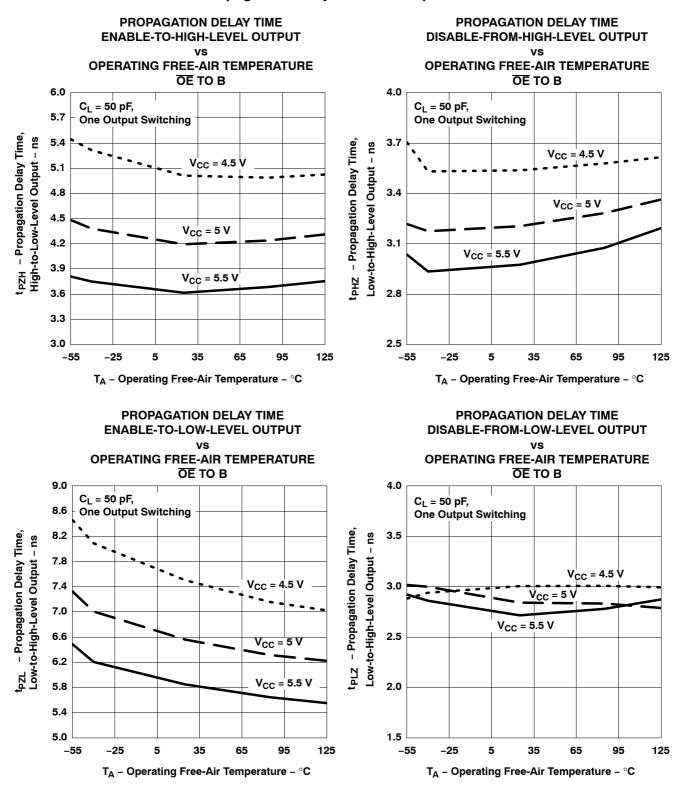

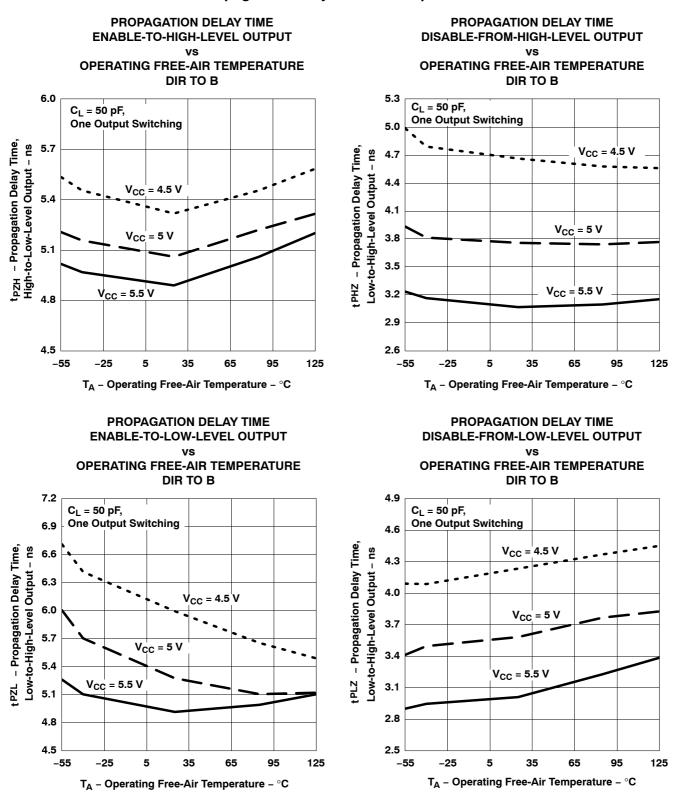

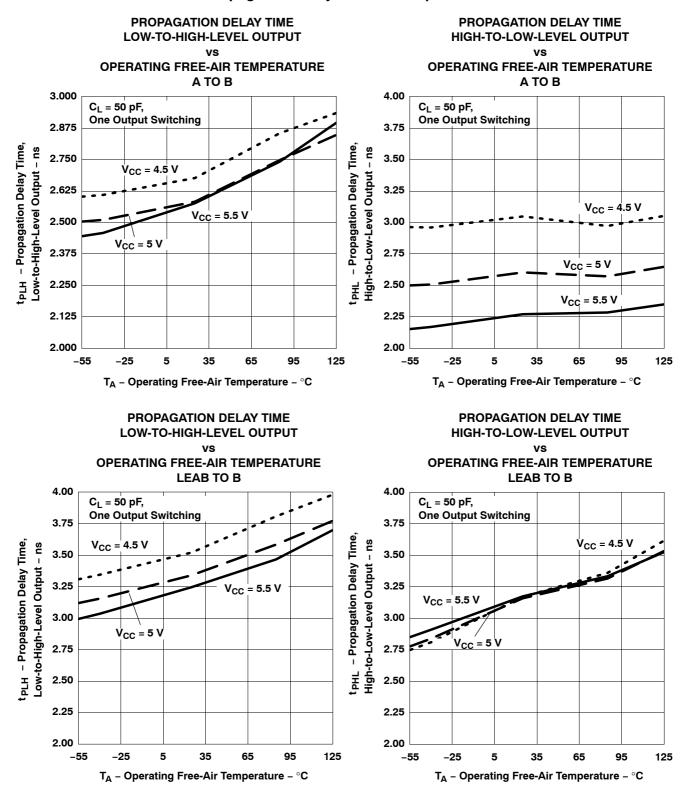

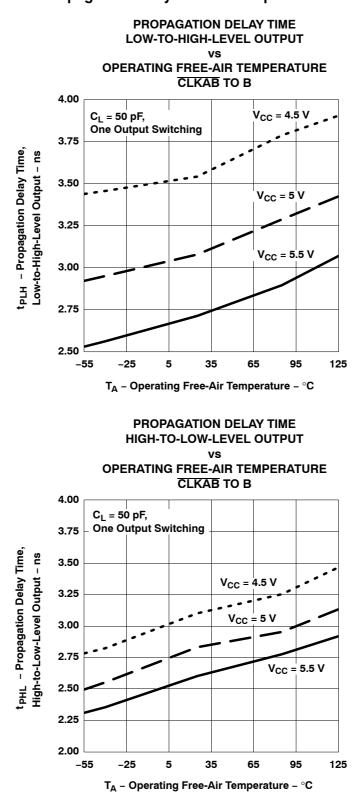

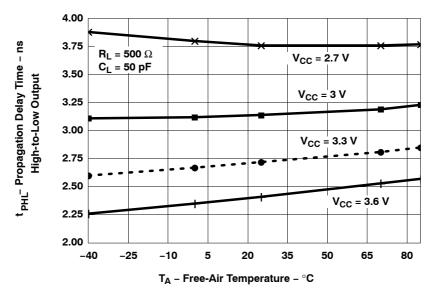

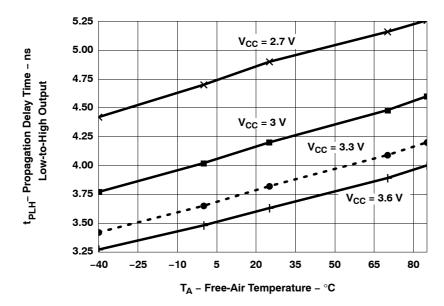

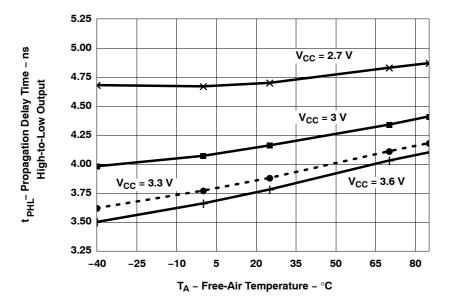

Figure 2 shows the propagation delay versus change in both temperature and supply voltage for an 'ABT16244A, 'FCT244A, and a 'F244 device. The graphs highlight two important aspects of the ABT logic family. First, ABT interface devices have extremely short propagation delay times. The figures clearly show the improvement in speed of an ABT device over that of a 74F and 74FCTA device. Second, the variance in speed with respect to both temperature and supply voltage is minimal for ABT. At low temperatures, the increase in CMOS performance compensates for the decrease in bipolar device strength. At high temperatures, the reverse occurs. This complementary performance of both CMOS and bipolar devices on a single chip results in a slope that is virtually flat across the entire temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C.

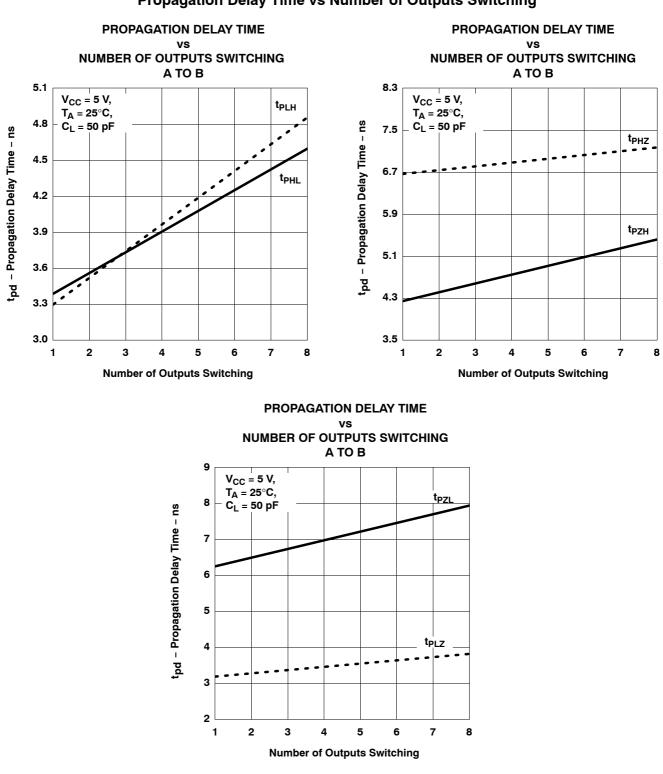

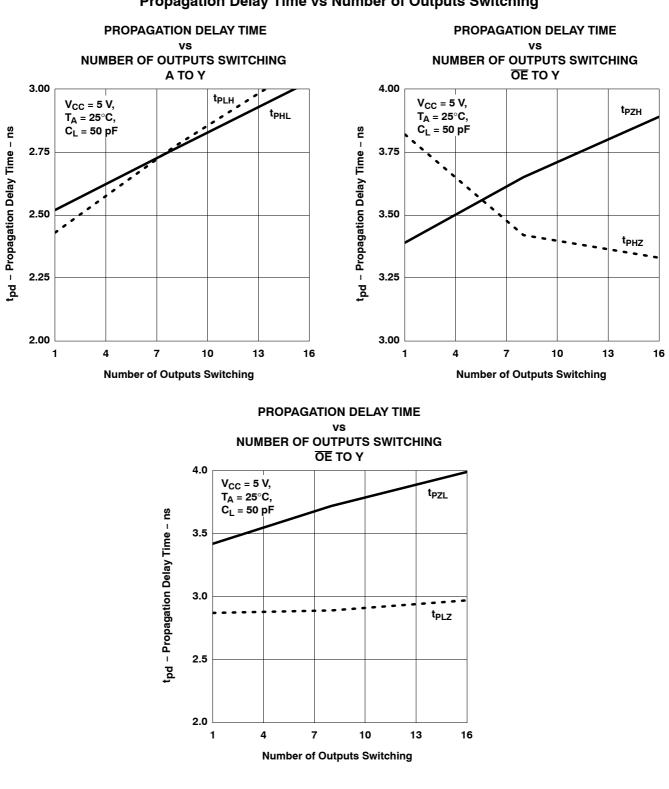

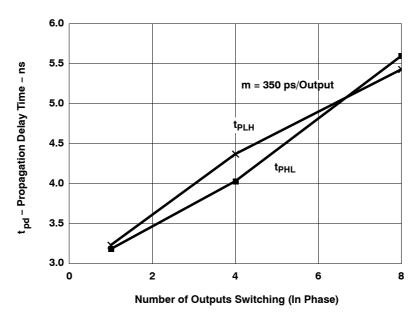

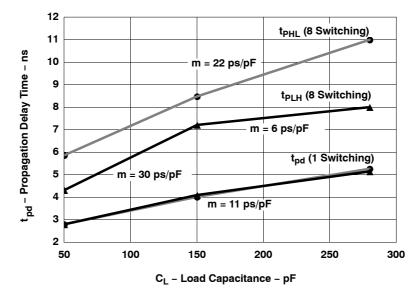

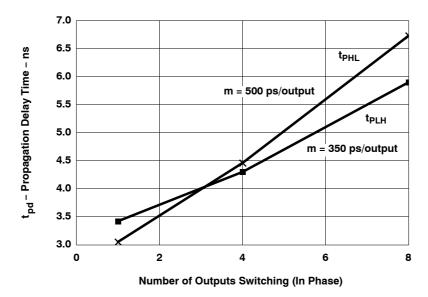

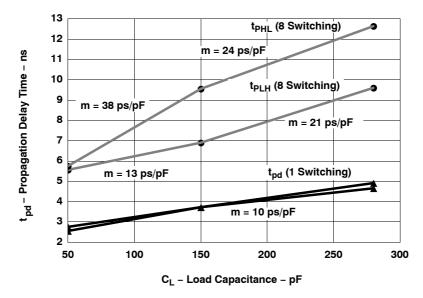

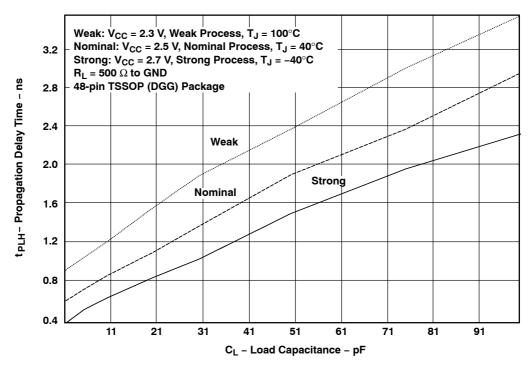

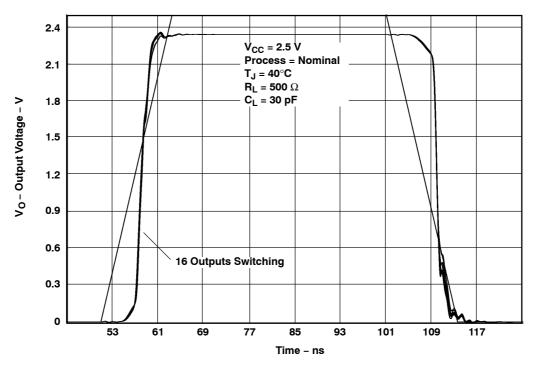

For most applications, the data sheet specifications may not provide all of the information a designer would like to see for a particular device. For instance, a designer might benefit from data such as propagation delay with multiple outputs switching or with various loads. This type of data is extremely difficult to test using automatic test equipment; therefore, it is provided in this document as family characteristics shown in Figure 2 and Figure 3.

To get a clear picture of where ABT stands in reference to other logic families, data is shown for a comparable (same function) 74F and 74FCTA device. It is clear that ABT is the designer's best choice for bus-interface applications that require consistent speed performance over various conditions.

NOTE: MAX is data sheet specification

Figure 1. Propagation Delay vs Operating Free-Air Temperature A to Y

NOTE: MAX is data sheet specification.

Figure 1. Propagation Delay vs Operating Free-Air Temperature A to Y (Continued)

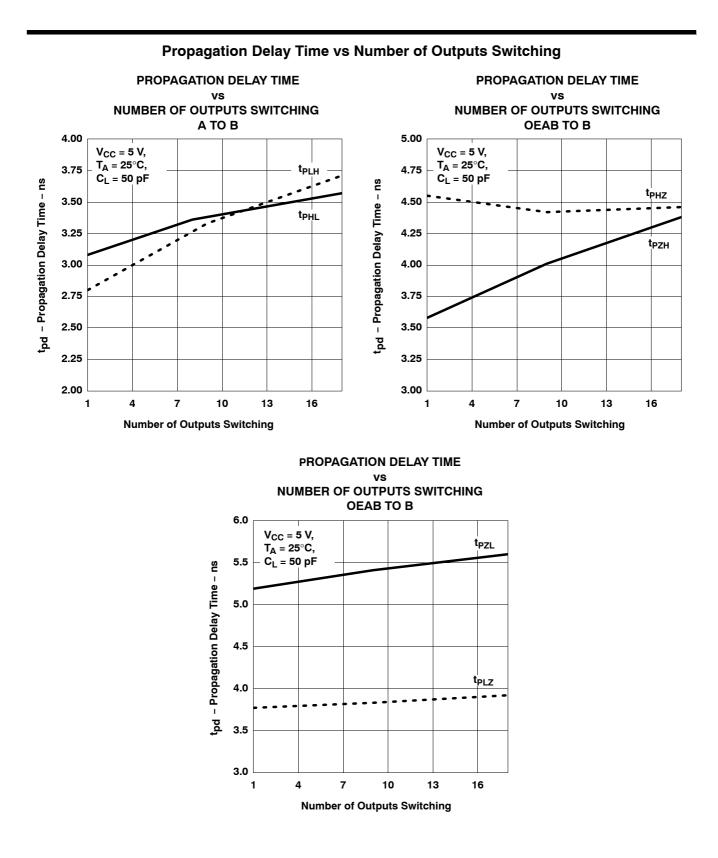

Figure 2. Propagation Delay Time vs Number of Outputs Switching

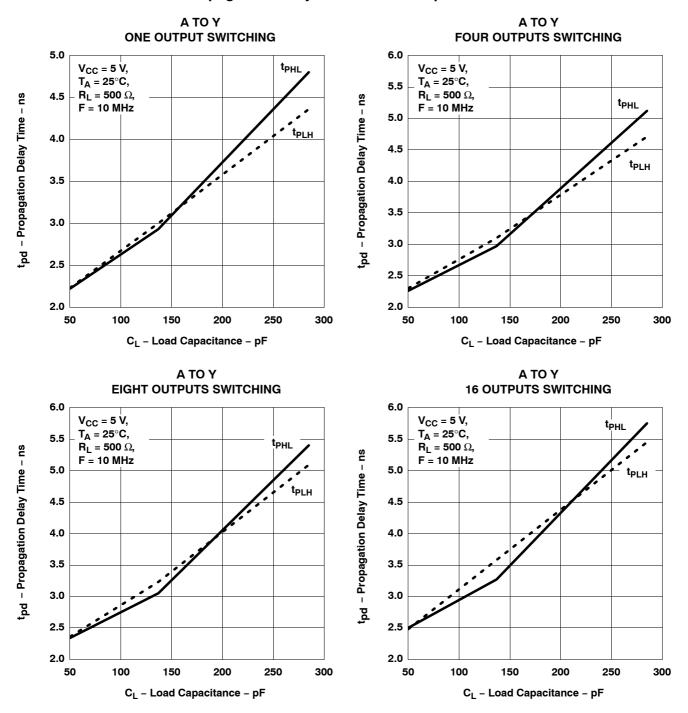

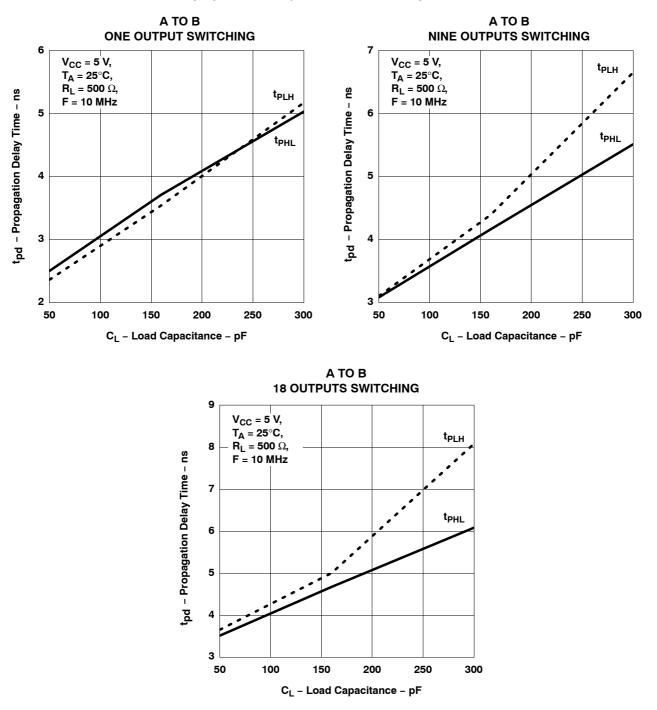

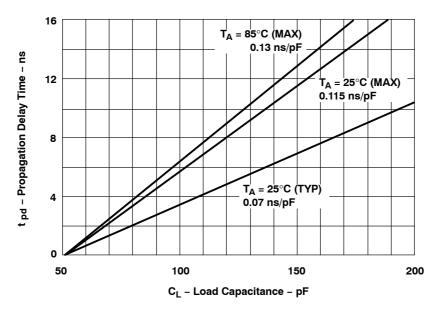

Figure 3. Propagation Delay vs Capacitive Load

## **Power Considerations**

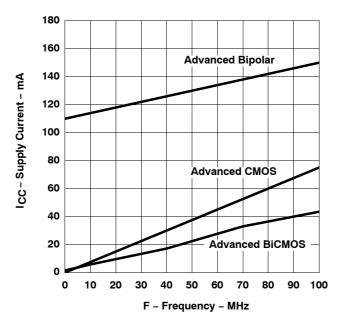

With the challenge to make systems more dense while improving performance comes the need to replace power-hungry devices without compromising speed. The ABT family of drivers provides a solution with low CMOS power consumption and high-speed bipolar technology on a single device.

There are two basic things to consider when calculating power consumption, static (dc) power, and dynamic power. Static power is calculated using the value of  $I_{CC}$  as shown in the data sheet. This is a dc value with no load on the outputs. To understand the relationship between pure CMOS, pure bipolar, and advanced BiCMOS for dc power rating, see Table 1, which shows the various data sheet values. The bipolar device shows the highest  $I_{CC}$  values, with little relief, regardless of the state of the outputs. This is not the case with ABT octals, which offer the low static power consumption of CMOS while in the high-impedance state, or when the outputs are high ( $I_{CCZ}$ ,  $I_{CCH}$ ).

| DADAMETED | TEST CONDITIONS                                                      |                  |  | 44    | 'FCT244 |        | SN74ABT244 |        |

|-----------|----------------------------------------------------------------------|------------------|--|-------|---------|--------|------------|--------|

| PARAMETER |                                                                      |                  |  | MAX   | MIN     | MAX    | MIN        | MAX    |

| Icc       | $V_{CC} = 5.5 \text{ V}, I_O = 0, V_I = V_{CC} \text{ or GND}$       | Outputs high     |  | 60 mA |         |        |            | 250 μΑ |

|           |                                                                      | Outputs low      |  | 90 mA |         |        |            | 30 mA  |

|           |                                                                      | Outputs disabled |  | 90 mA |         |        |            | 250 μΑ |

|           | $V_{CC}$ = maximum, V $\geq$ V_{CC} – 0.2 V, V $\leq$ V_{CC} – 0.2 V |                  |  |       |         | 1.5 mA |            |        |

| Table 1. | Supply | Current |

|----------|--------|---------|

|----------|--------|---------|

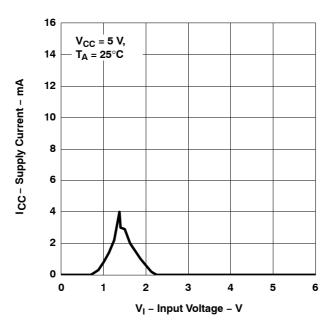

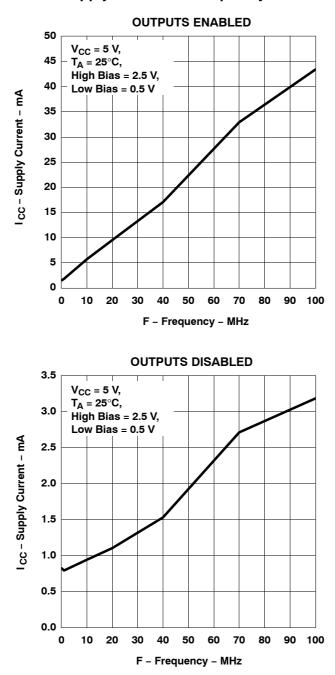

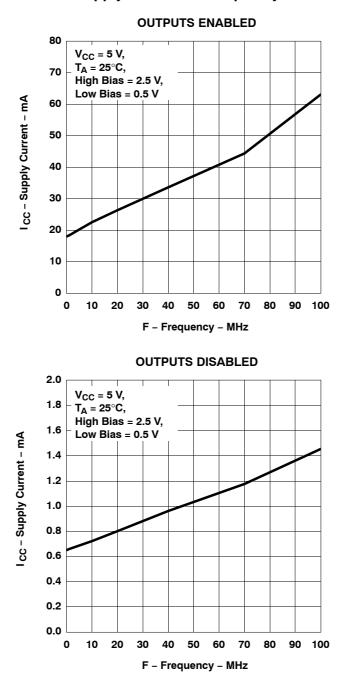

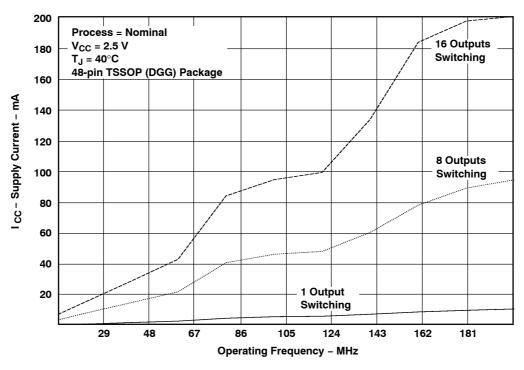

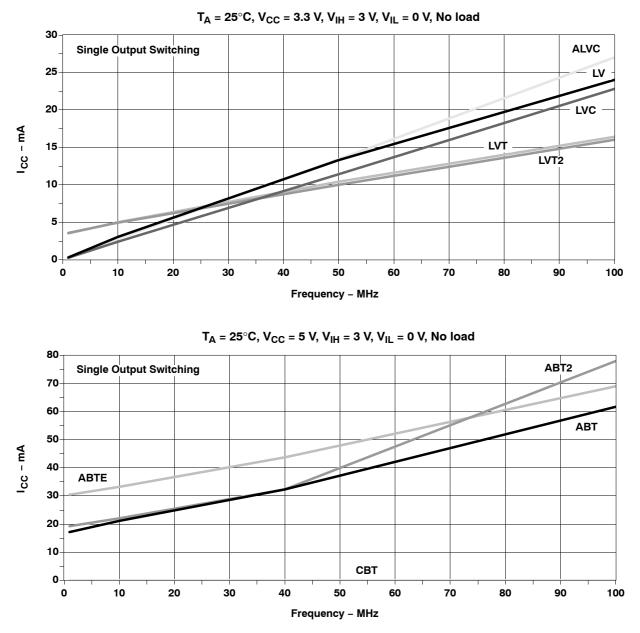

Dynamic power involves the charging and discharging of internal capacitances, as well as the external load capacitance. It is this dynamic component that makes up the majority of the total power dissipation. Figure 4 shows power as a function of frequency for ABT, FCT, and F devices. Although bipolar devices tend to have extremely high static power, there is a point on the frequency curve, commonly referred to as the crossover point, where the CMOS device no longer consumes less power. With ABT devices, the power increase at higher frequencies is less than that of the pure CMOS FCT.

Figure 4. Supply Current vs Frequency

The use of bipolar transistors in the output stage is advantageous in two ways. First, the voltage swing is less than with a CMOS output, reducing the power consumed when charging or discharging the external load. Second, bipolar transistors are capable of turning off more efficiently than CMOS transistors, thus reducing the flow of current from  $V_{CC}$  to GND. Combined, these features allow for better power performance at high frequencies.

#### **Input Characteristics**

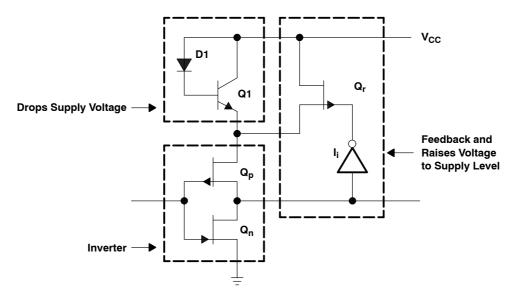

ABT bus-interface devices are designed to ensure TTL-compatible input levels switching between 0.8 V and 2 V (typically 1.5 V). Additionally, these inputs are implemented with CMOS circuitry, resulting in high impedance (low leakage) and low capacitance, which reduces overall bus loading. This section is an overview of the circuitry utilized for a typical ABT input, the corresponding electrical characteristics, and guidelines for proper termination of unused inputs.

#### **ABT Input Circuitry**

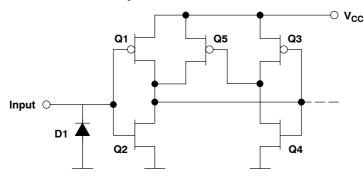

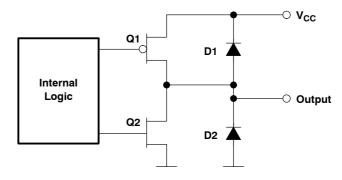

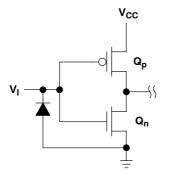

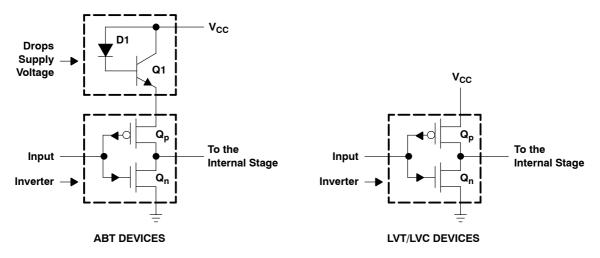

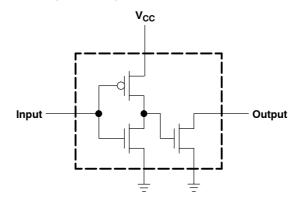

Figure 5 shows a typical ABT input schematic. A pure CMOS-input threshold is normally set at one-half of  $V_{CC}$ . To shift the threshold voltage to be centered around 1.5 V (see Figure 6), the supply voltage of the input stage is dropped by the diode, D1, and the transistor, Q1. Reducing the voltage at the source of  $Q_p$  enables it to turn off more efficiently when flow is from  $V_{CC}$  to GND ( $\Delta I_{CC}$ ). When the input is in the low state,  $Q_r$  raises the voltage of the source of  $Q_p$  to  $V_{CC}$  to ensure proper operation of the following stage. This feedback circuit provides approximately 100 mV of input hysteresis, which increases the noise margin and helps ensure the device is free from oscillations when operated within specified input ramp rates.

Figure 5. Simplified Input Stage of an ABT Circuit

Figure 6. Output Voltage vs Input Voltage

## Input Current Loading

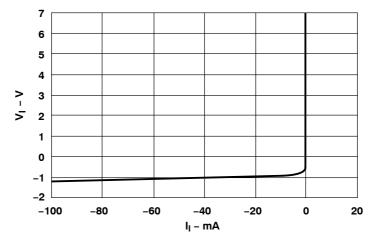

The utilization of submicron  $(0.8-\mu m)$  CMOS technology for the input stage of ABT devices causes minimal loading of the system bus due to low leakage currents and low capacitance. The small geometries of the EPIC-IIB process have resulted in capacitances as low as 3 pF for inputs and 8 pF for C<sub>io</sub> of a transceiver. Figure 7 and Table 2 indicate the low input current performance and specifications. Considering this low capacitance along with the negligible input current, systems designers can decrease their overall bus loading.

Figure 7. Input Current vs Input Voltage

| DADAMETED                 | TEST CONDITIONS   |                                        | T <sub>A</sub> = 25°C |     |     | SN54ABT245 |     | SN74ABT245 |      |    |

|---------------------------|-------------------|----------------------------------------|-----------------------|-----|-----|------------|-----|------------|------|----|

| PARAMETER TEST CONDITIONS |                   | MIN                                    | TYP                   | MAX | MIN | MAX        | MIN | MAX        | UNIT |    |

| łį                        | $V_{CC} = 5.5 V,$ | V <sub>I</sub> =V <sub>CC</sub> or GND |                       |     | ±1  |            | ±1  |            | ±1   | μA |

| I <sub>OZH†</sub>         | $V_{CC} = 5.5 V,$ | V <sub>O</sub> =2.7 V                  |                       |     | 50  |            | 50  |            | 50   | μA |

| l <sub>ozl</sub> †        | $V_{CC} = 5.5 V,$ | V <sub>O</sub> =0.5 V                  |                       |     | -50 |            | -50 |            | -50  | μA |

<sup>†</sup> The parameters I<sub>OZH</sub> and I<sub>OZL</sub> include the input leakage current.

## Supply Current Change (Alcc)

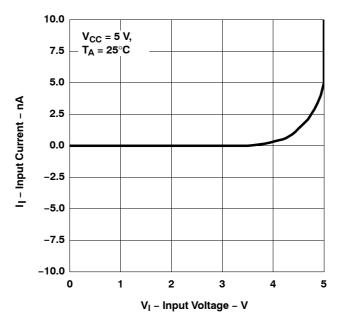

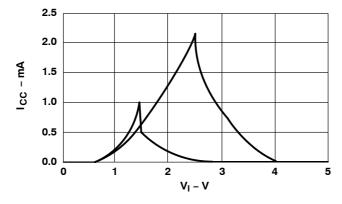

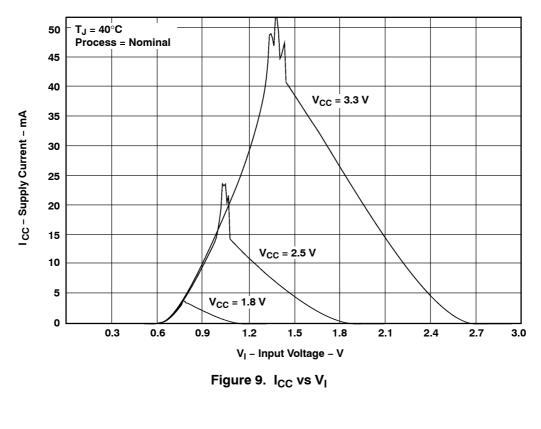

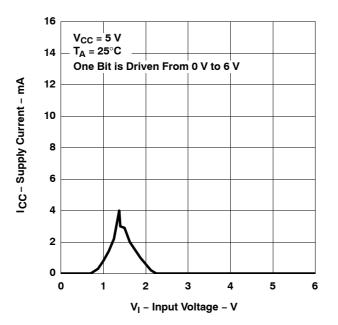

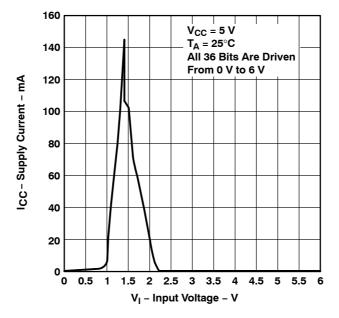

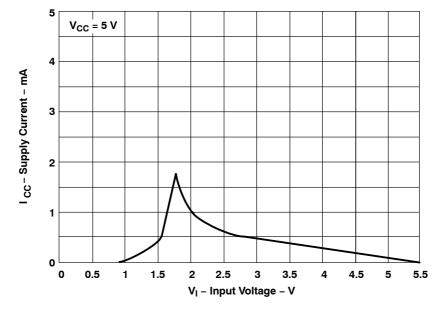

Because ABT devices utilize a CMOS-input stage but operate in a TTL-level signal environment, there is a current specification unique to this set of conditions known as  $\Delta I_{CC}$ . Given a CMOS inverter with the input voltage set so that both the p and n channel devices are on, current flows from  $V_{CC}$  to GND. This can occur when the input to an ABT device is at a valid high level (>2 V), which turns on the n-channel, but not high enough to completely turn off the p-channel device. The current that flows under these conditions is specified in the data sheet ( $\Delta I_{CC}$ ) and is measured one input at a time with the input voltage set at 3.4 V. Figure 8 shows the change in  $I_{CC}$  as the input is ramped from 0 V to 5 V. For ABT non-storage devices, a feature is added that turns off the input when the outputs are disabled to reduce power consumption (see Table 3 for an example. Refer to individual data sheets for this specification).

Figure 8. Supply Current vs Input Voltage

| Table 3. | Supply | Current | Change | (∆l <sub>CC</sub> ) |

|----------|--------|---------|--------|---------------------|

|----------|--------|---------|--------|---------------------|

| DADAMETER                  | TEST CONDITIONS                             |                  | T <sub>A</sub> = 25°C |     | SN54ABT244 |     | SN74ABT244 |     |      |

|----------------------------|---------------------------------------------|------------------|-----------------------|-----|------------|-----|------------|-----|------|

| PARAMETER                  |                                             |                  | MIN                   | MAX | MIN        | MAX | MIN        | MAX | UNIT |

| $\Delta I_{CC}^{\ddagger}$ | V <sub>I</sub> = 5.5 V, One input at 3.4 V, | Outputs enabled  |                       | 1.5 |            | 1.5 |            | 1.5 | mA   |

|                            | Other inputs at $V_{CC} \text{ or } GND$    | Outputs disabled |                       | 50  |            | 50  |            | 50  | μA   |

<sup>‡</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

## **Proper Termination of Unused Inputs**

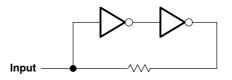

With advancements in speed, logic devices have become more sensitive to slow input edge rates. A slow input edge rate, coupled with the noise generated on the power rails when the output switches, can cause excessive output glitching or, in some cases, oscillations. Similar situations can occur if an unused input is left floating or not being actively held at a valid logic level.

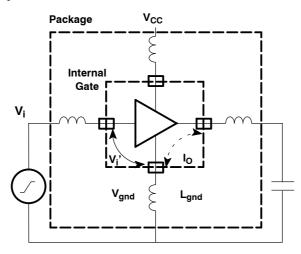

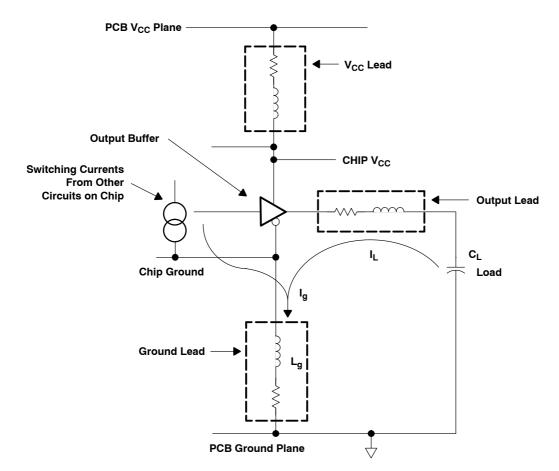

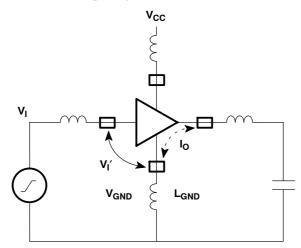

These problems are due to voltage transients induced on the device's power system as the output load current (I<sub>O</sub>) flows through the parasitic lead inductances during switching (see Figure 9). Since the device's internal power-supply nodes are used as voltage references throughout the integrated circuit, the inductive voltage spikes ( $V_{gnd}$ ) affect the way signals appear to the internal gate structures. For instance, as the voltage at the device's ground node rises, the input signal ( $V_i$ ') appears to decrease in magnitude. This undesirable phenomena can erroneously change the output's transition if a threshold violation takes place.

In the case of a slowly rising input edge, if the ground movement is large enough, the apparent signal,  $V_i$ ', at the device appears to be driven back through the threshold and the output starts to switch in the opposite direction. If worst-case conditions prevail (simultaneously switching all of the outputs with large transient load currents) the slow input edge is repeatedly driven back through the threshold, resulting in output oscillation.

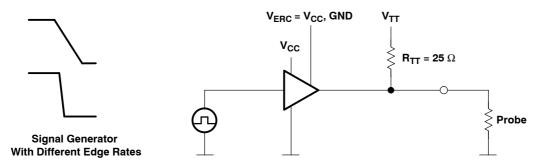

ABT devices are recommended to have input edge rates faster than 5 ns/V for standard parts, and 10 ns/V for the Widebus<sup>TM</sup> series of products when the outputs are enabled. A critical area for this edge rate is in the transition region between 1 V and 2 V. It is also recommended to hold inputs or I/O pins at a valid logic high or low when they are not being used or when the part driving them is in the high-impedance state.

Figure 9. Sample Input/Output Model

## **Output Characteristics**

The current trend is consolidation of the functionality of multiple logic devices into complex, high pin-count ASICs and programmables. There are a number of important advantages for utilizing bus-interface devices in standard high-volume packages. These include the need for high drive capability and good signal integrity. The use of bipolar circuitry in the output stage makes it possible to provide these requirements, along with increased speed, using the ABT family.

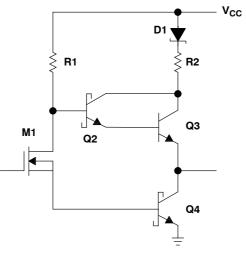

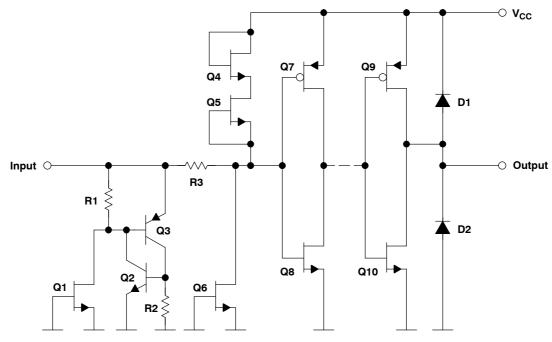

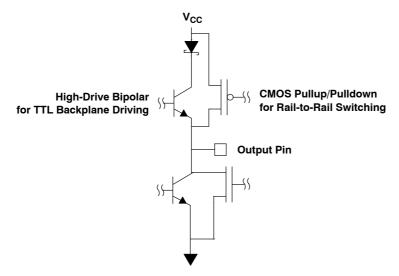

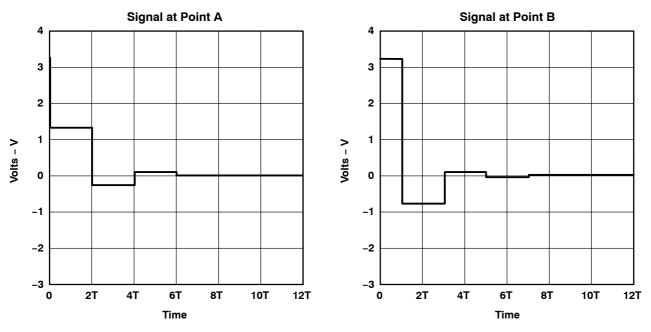

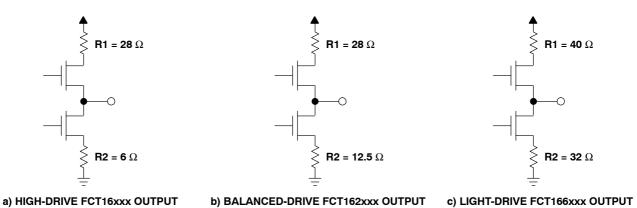

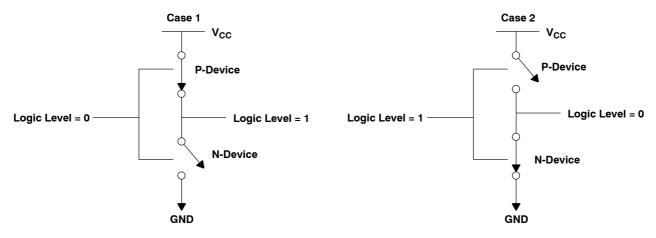

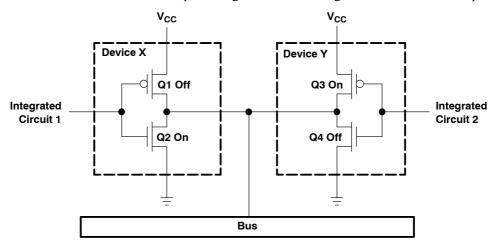

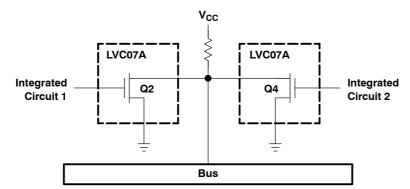

Figure 10 shows a simplified schematic of an ABT output stage. Data is transmitted to the gate of M1, which acts as a simple current switch. When M1 is turned on, current flows through R1 and M1 to the base of Q4, turning it on and driving the output low. At the same time, the base of Q2 is pulled low, thus turning off the upper output. For a low-to-high transition, the gate of M1 must be driven low, turning M1 off. Current through R1 charges the base of Q2, pulling it high and turning on the Darlington pair, consisting of Q2 and Q3. Meanwhile, with its supply of base drive cut off, Q4 turns off, and the output switches from low to high. R2 is used to limit output current in the high state, and D1 is a blocking diode used to prevent reverse current flow in specific power-down applications.

Figure 10. Simplified ABT Output Stage

A clear advantage of using bipolar circuitry in the output stage (as opposed to CMOS) is the reduced voltage swing. This helps to lower ground noise and reduce power consumption. Refer to *Signal Integrity* and *Power Considerations* in this document for further information.

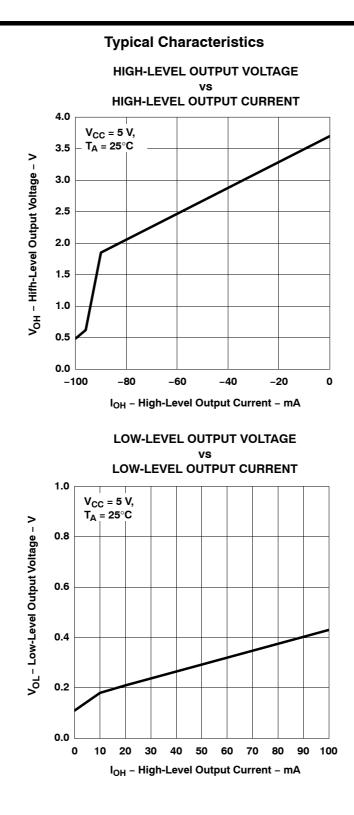

## **Output Drive**

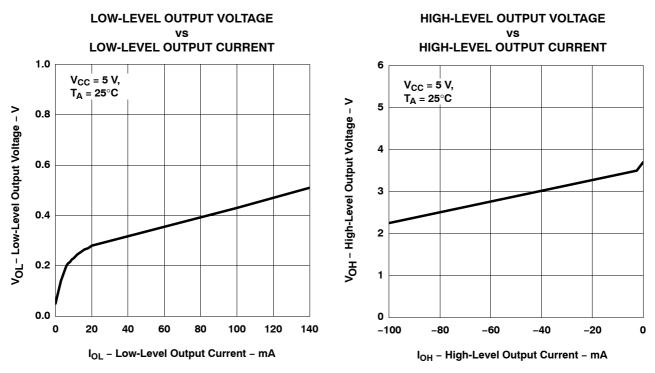

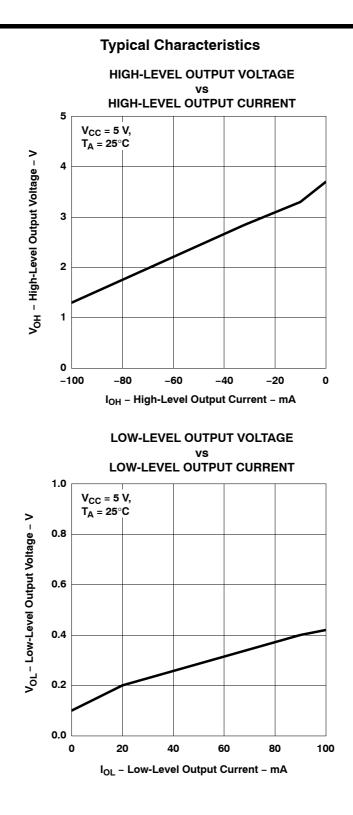

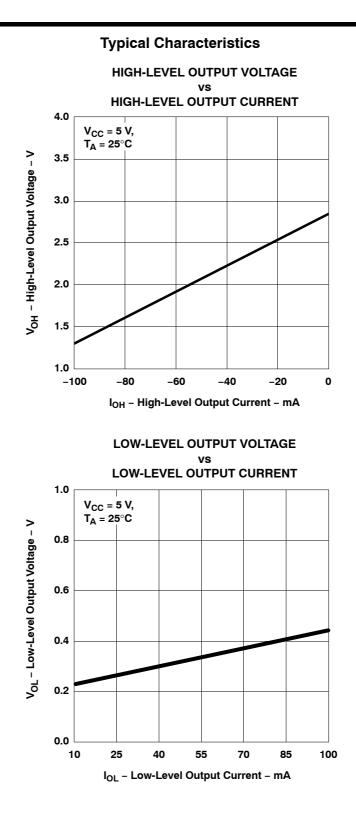

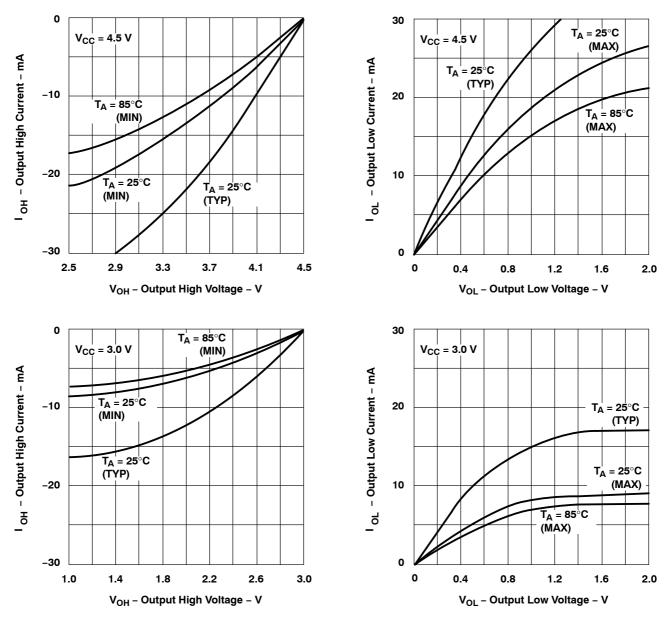

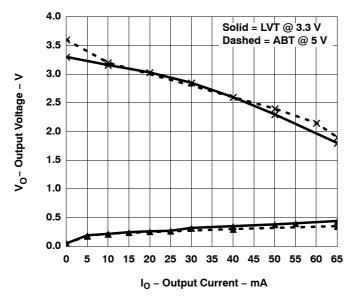

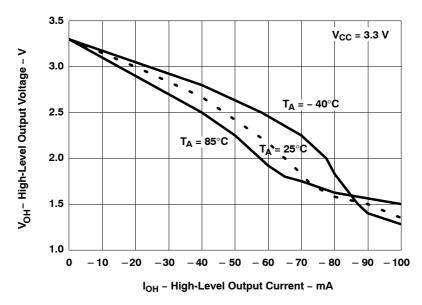

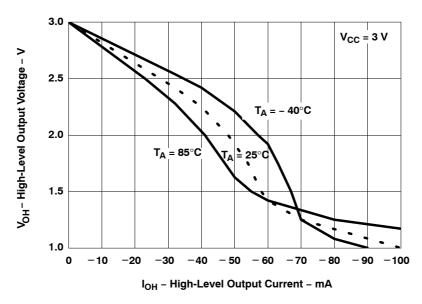

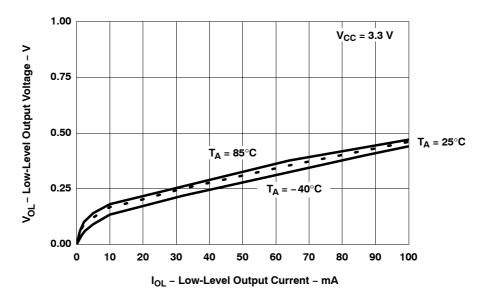

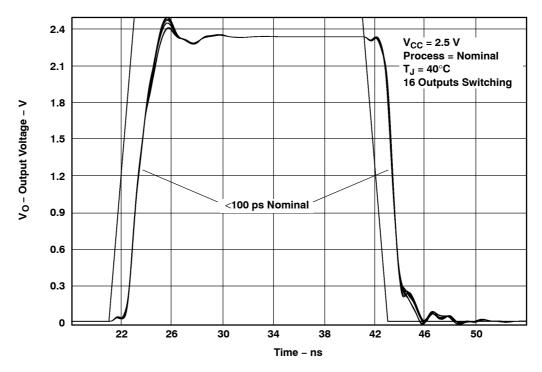

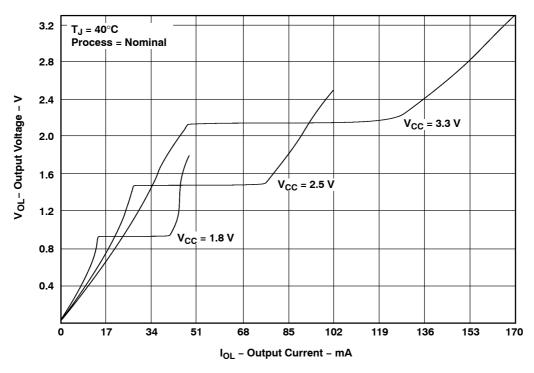

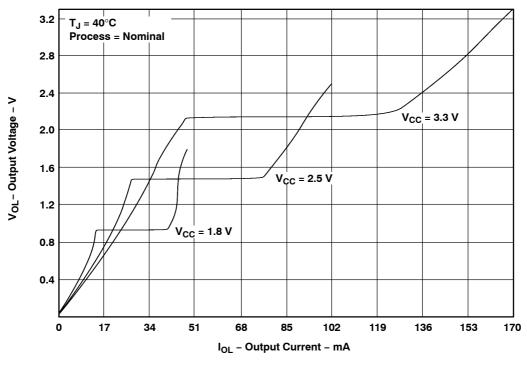

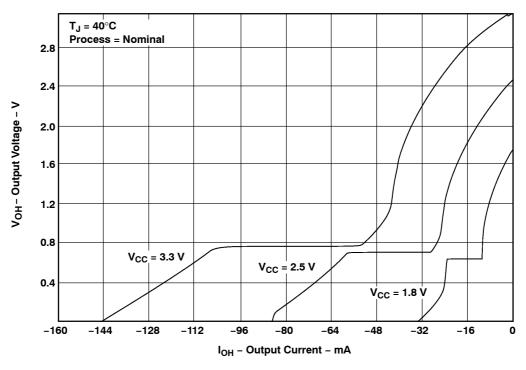

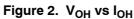

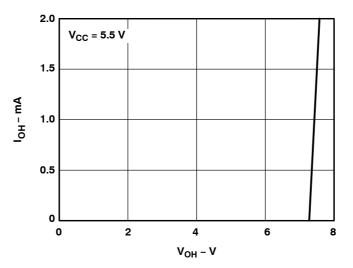

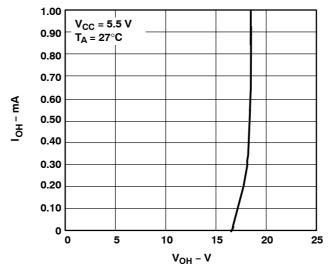

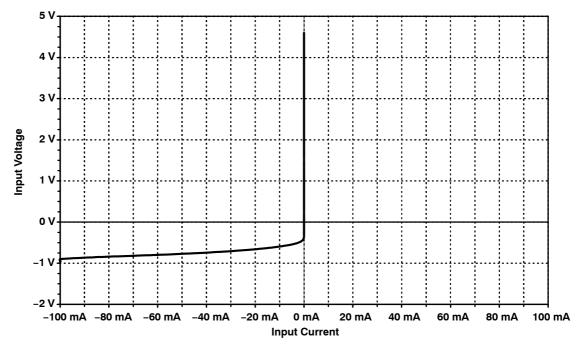

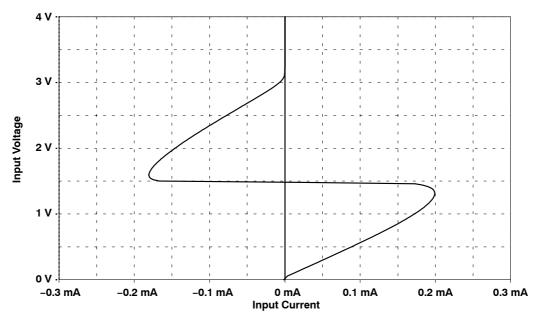

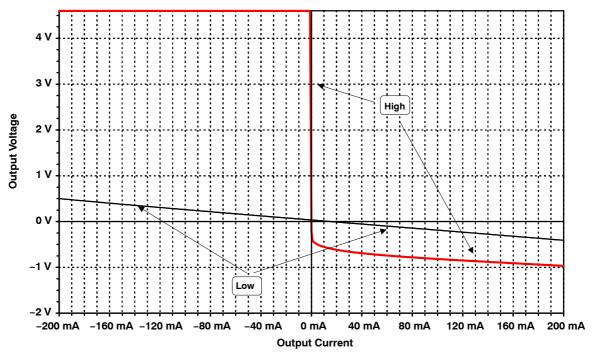

The  $I_{OH}$  and  $I_{OL}$  curves for a typical ABT output are shown in Figure 11. With a specified  $I_{OL}$  of 64 mA and  $I_{OH}$  of -32 mA, ABT accommodates many standard backplane specifications. However, these devices are capable of driving well beyond these limits. This is important when considering switching a low-impedance backplane on the incident wave.

Figure 11. Typical ABT Output Characteristics

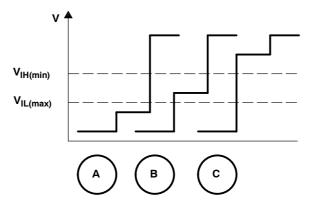

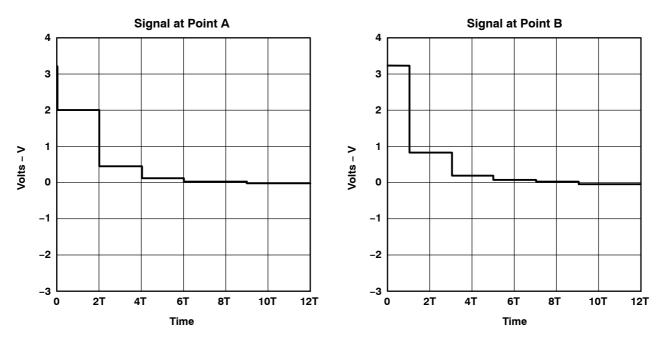

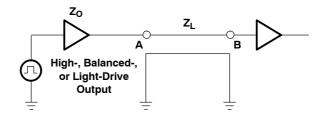

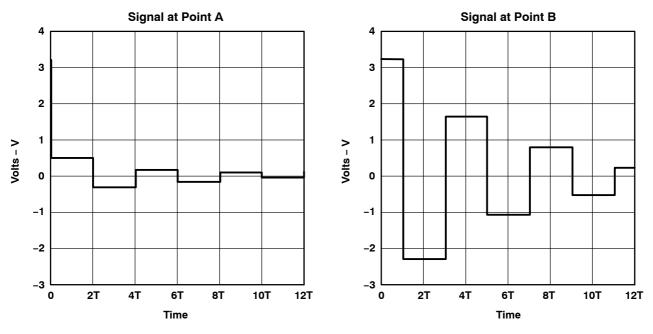

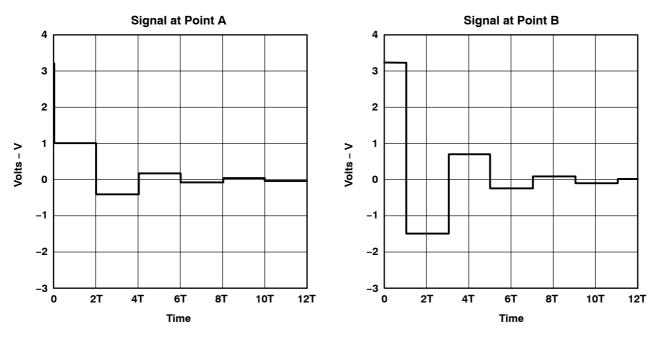

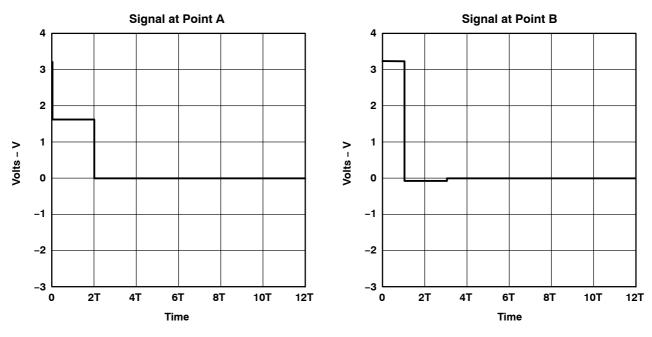

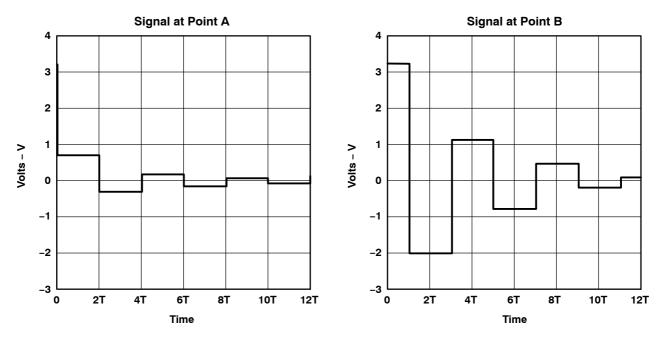

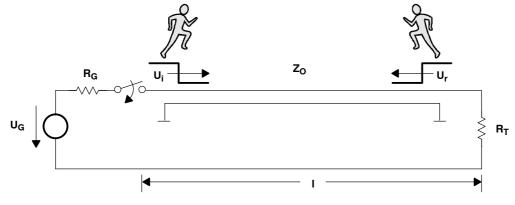

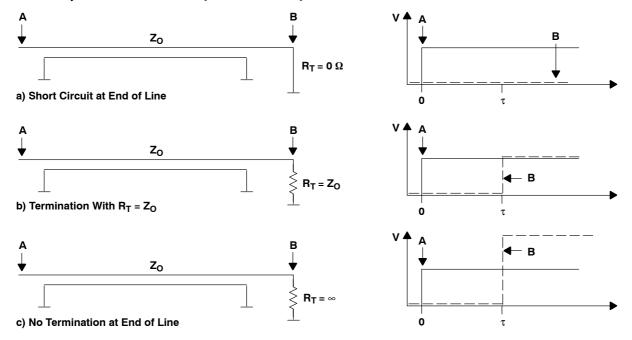

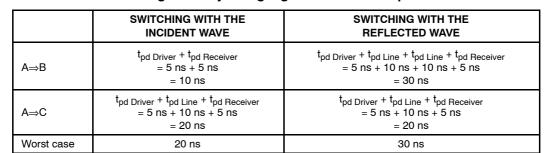

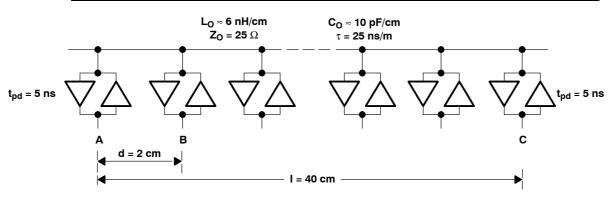

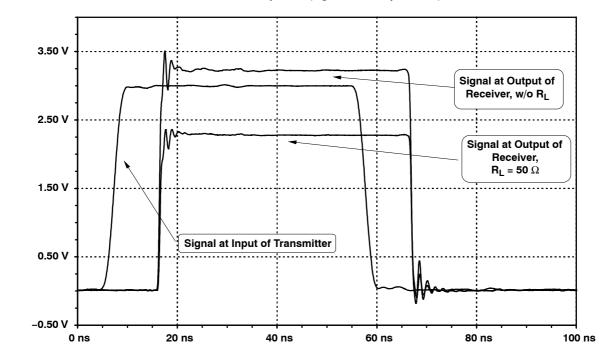

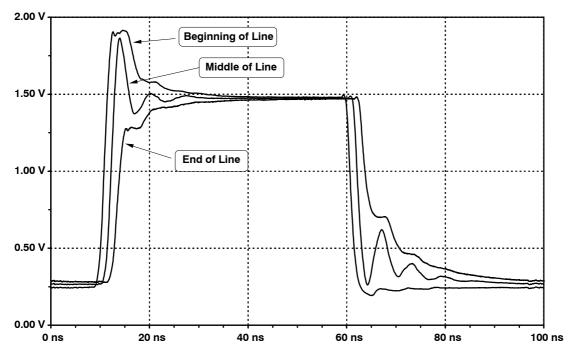

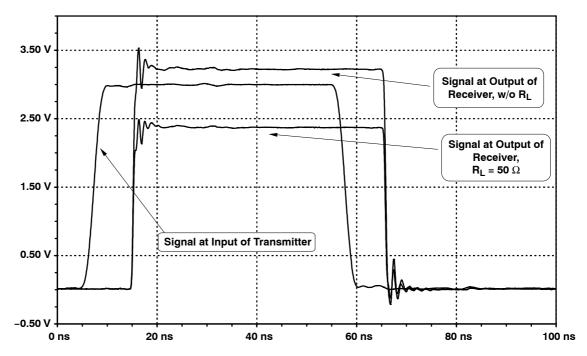

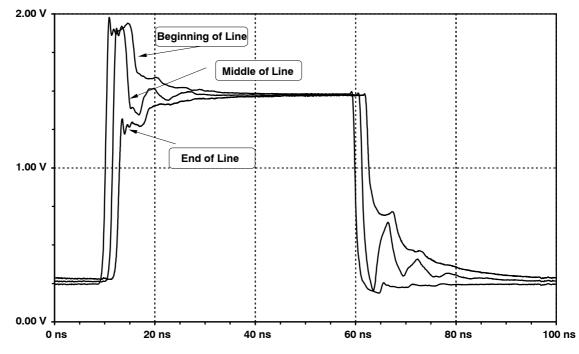

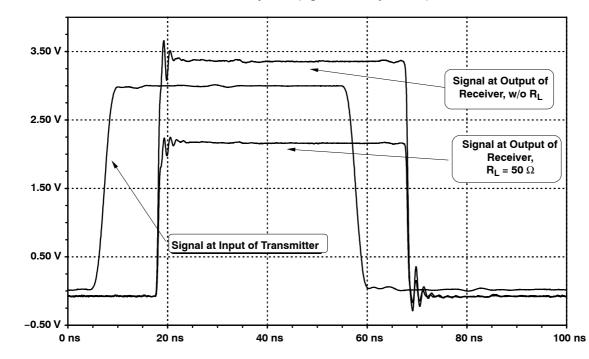

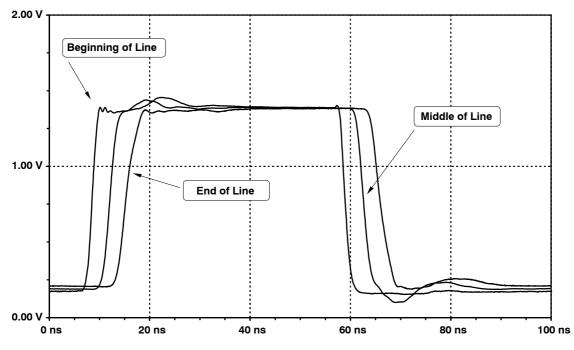

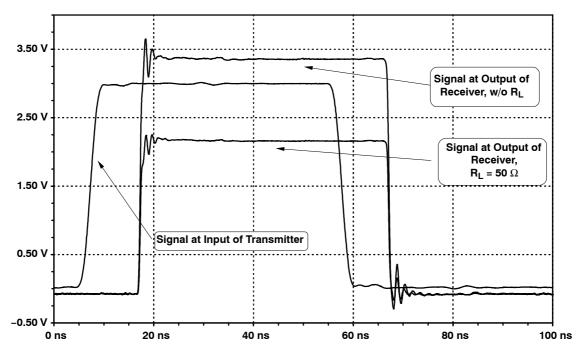

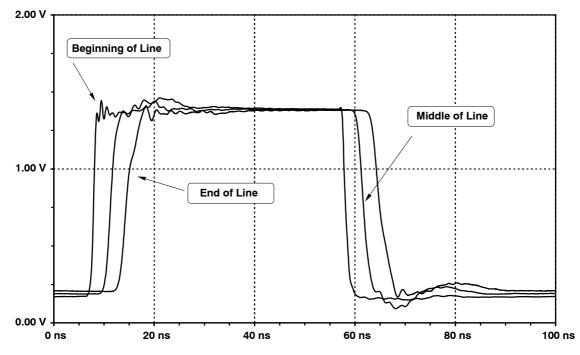

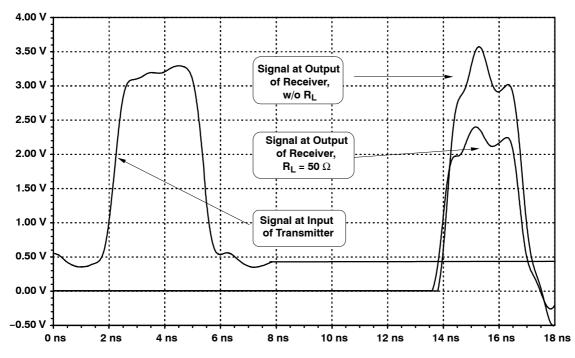

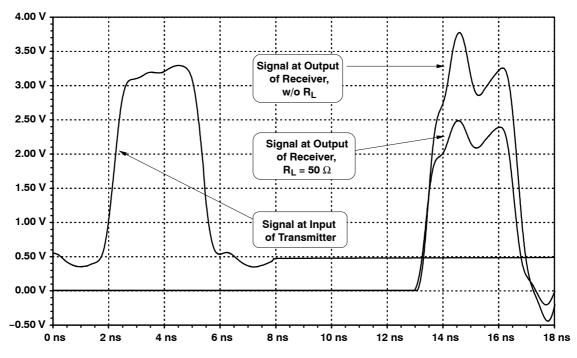

Incident-wave switching ensures that for a given transition (either high-to-low or low-to-high) the output reaches a valid  $V_{IH}$  or  $V_{IL}$  level on the initial wave front (i.e., does not require reflections). Figure 12 shows the problems a designer might encounter when a device does not switch on the incident wave. A shelf below  $V_{IL(max)}$ , signal A, causes the propagation delay to slow by the amount of time it takes for the signal to reach the receiver and reflect back. Signal B shows the case in which there is a shelf in the threshold region. When this happens, the input to the receiver is uncertain and could cause several problems associated with slow input edges, depending on the length of time the shelf remains in this region. A signal as shown in example C does not cause a problem because the shelf does not occur until the necessary  $V_{IH}$  level has been attained.

Figure 12. Reflected Wave Switching

Using typical  $V_{OH}$  and  $V_{OL}$  values along with data points from the curves, ABT devices can typically drive lines in the 25- $\Omega$  range on the incident wave.

For a low-to-high transition,  $(I_{OH} = 85 \text{ mA} @ V_{OH} = 2.4 \text{ V})$

$$Z_{LH} = \frac{V_{OH}(min) - V_{OL}(typ)}{I_{OH}} = \frac{2.4 \text{ V} - 0.3 \text{ V}}{85 \text{ mA}} - 25 \Omega$$

(1)

For a high-to-low transition, (IoL= 135 mA @ VoL= 0.5 V)

$$Z_{\rm HL} = \frac{V_{\rm OH}(\rm typ) - V_{\rm OL}(\rm max)}{I_{\rm OL}} = \frac{3.5 \,\rm V - 0.5 \,\rm V}{135 \,\rm mA} - 22 \,\Omega \tag{2}$$

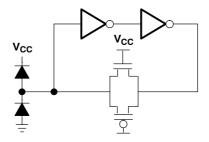

#### **Partial Power Down**

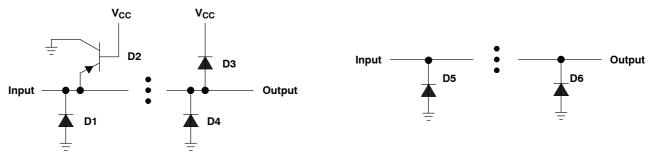

One application, addressed when designing the ABT family, is partial system power down. When using a standard CMOS device, there is a path from either the input or the output (or both) to  $V_{CC}$ . This prevents partial power down for such applications as hot-card insertion without adding current limiting components. This is not the case with ABT as these paths have been eliminated with the use of blocking diodes. Figure 13 shows functionally equivalent schematics of the input structures for CMOS and ABT devices.

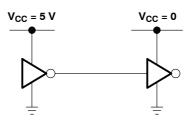

Consider the situation shown in Figure 14. The driving device is powered with  $V_{CC} = 5$  V, while the receiving device is powered down ( $V_{CC} = 0$ ). If these devices are CMOS, the receiver can be powered up through diode D2 when the driver is in a high state. ABT devices do not have a comparable path and are thus immune to this problem, making them more desirable for this application.

(a) CMOS EQUIVALENT INPUT STRUCTURE

(b) ABT EQUIVALENT INPUT STRUCTURE

Figure 13. Simplified Input Structures for CMOS and ABT Devices

Figure 14. Example of Partial System Power Down

## **Signal Integrity**

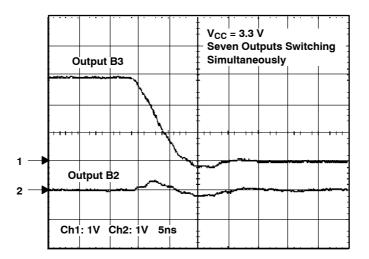

A frequent concern of system designers is the performance degradation of ICs when outputs are switched. TI's priority when designing the ABT bus-interface family was to insure signal integrity and eliminate the need for excess settling time of an output waveform. This section addresses the simultaneous switching performance of both the ABT octals and the Widebus functions.

#### Simultaneous-Switching Phenomenon

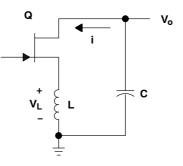

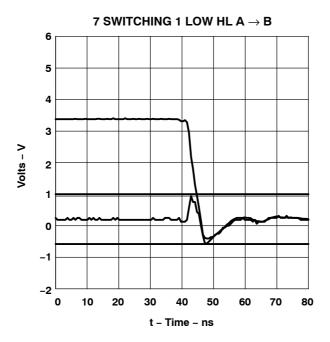

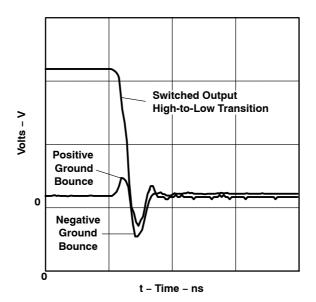

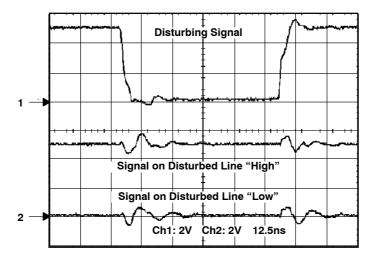

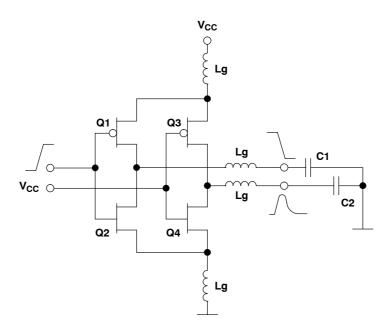

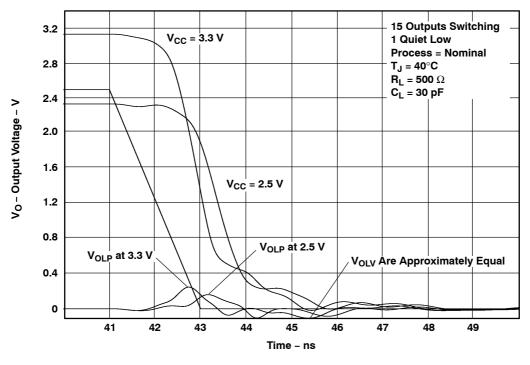

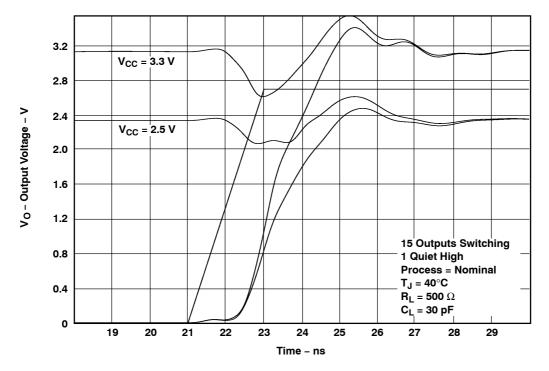

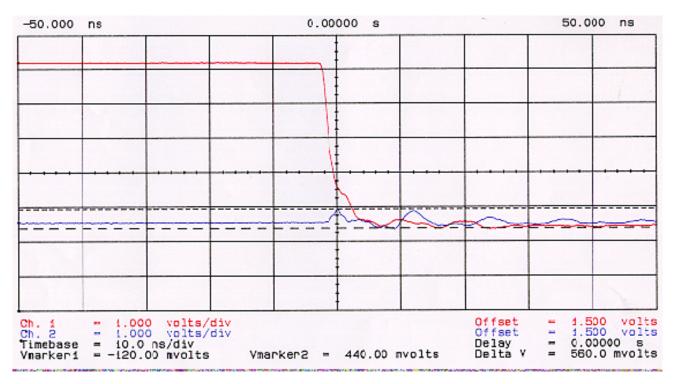

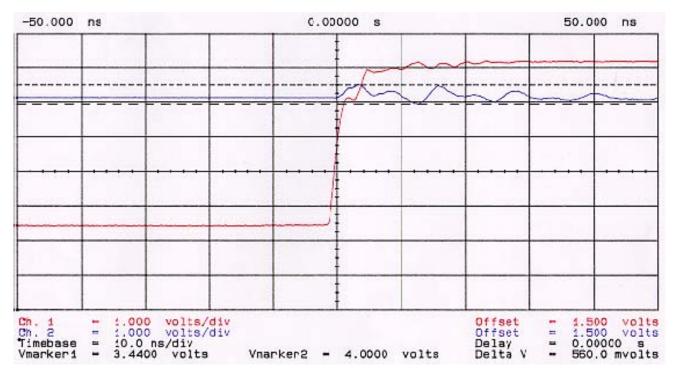

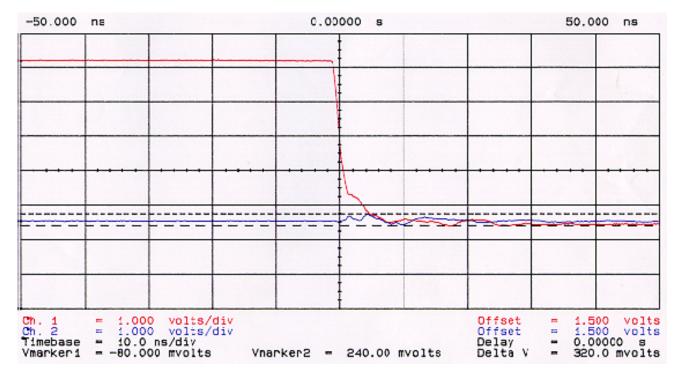

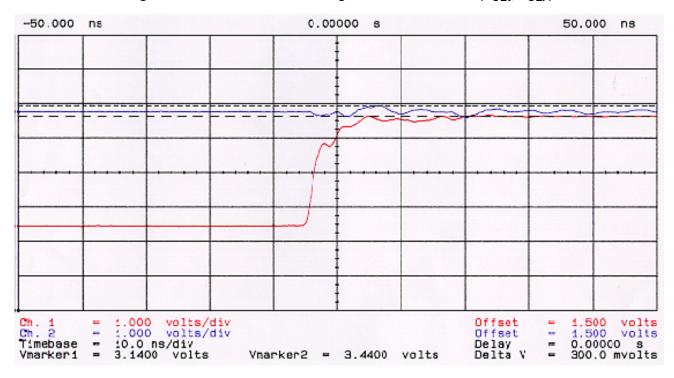

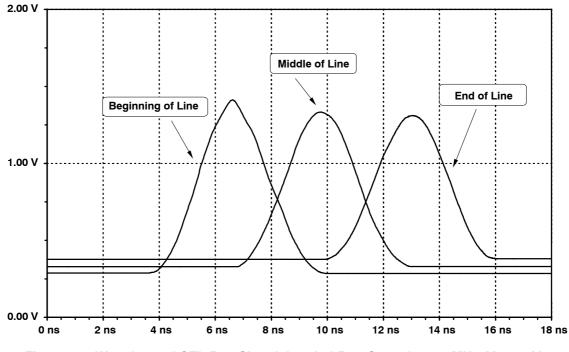

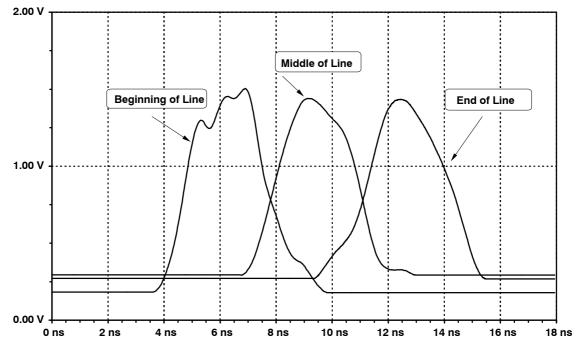

Figure 15 shows a simple model of an output pin, including the associated capacitance of the output load and the inherent inductance of the ground lead. The voltage drop across the GND inductor,  $V_L$ , is determined by the value of the inductance and the rate of change in current across the inductor. When multiple outputs are switched from high to low, the transient current (di/dt) through the GND inductor generates a difference in potential on the chip ground with respect to the system ground. This induced GND variation can be observed indirectly as shown in Figure 16. The voltage output low peak ( $V_{OLP}$ ) is measured on one quiet output when all others are switched from high to low.

Figure 15. Simultaneous-Switching Output Model

NOTE: V<sub>OLP</sub> = Maximum (peak) voltage induced on a quiescent low-level output during switching of other outputs

## Figure 16. Simultaneous-Switching-Noise Waveform

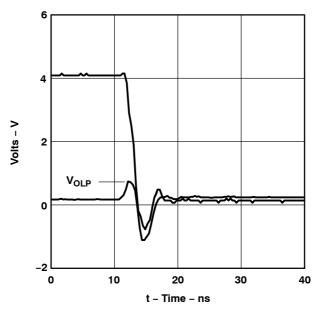

A similar phenomena occurs with respect to the  $V_{CC}$  plane on a low-to-high transition, known as voltage output high valley ( $V_{OHV}$ ). Most problems are associated with a large  $V_{OLP}$  because the range for a logic 0 is much less than the range for a logic 1, as shown in Figure 17. For a comprehensive discussion of simultaneous switching, see *Simultaneous Switching Evaluation and Testing*, Section 4.1, in the *Advanced CMOS Logic (ACL) Designer's Handbook*, literature number SCAA001B.

The impact of these voltage noise spikes on a system can be extreme. The noise can cause loss of stored data, severe speed degradation, false clocking, and/or reduction in system noise immunity. For an overview of how propagation delay is affected by the switching of multiple outputs, please refer to *ac Performance* in this document.

Figure 17. TTL DC Noise Margin

#### **Simultaneous Switching Solutions**

Some methods an IC manufacturer can use to reduce the effects of simultaneous switching include: reducing the inductance of the power pins, adding multiple power pins, and controlling the turn on of the output. These techniques are described in the *Advanced CMOS Logic (ACL) Designer's Handbook*, literature number SCAA001B.

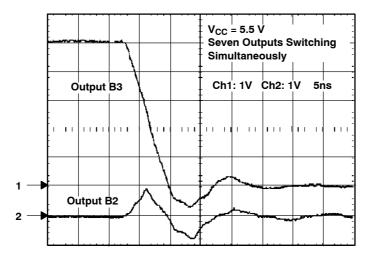

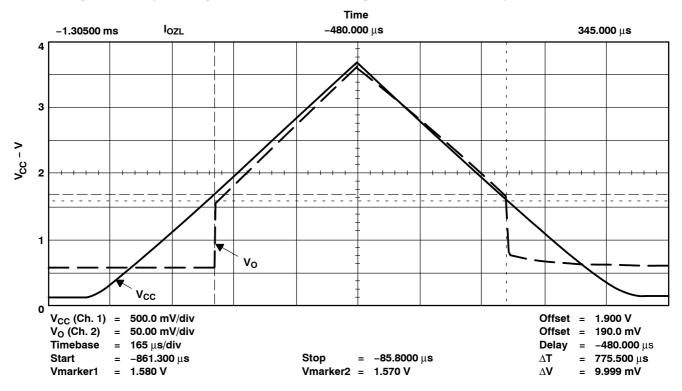

Octal ABT devices employ the standard end-pin GND and  $V_{CC}$  configuration, while maintaining acceptable simultaneous switching performance, as shown in Figure 18. This is due to the TTL-level output swing (0.3–3 V) and a controlled feedback, which limits the base drive to the lower output.

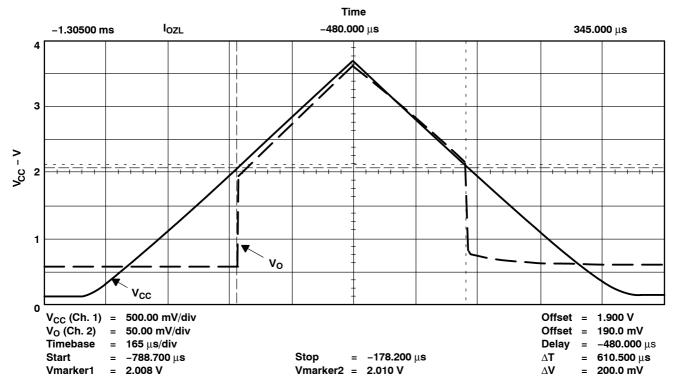

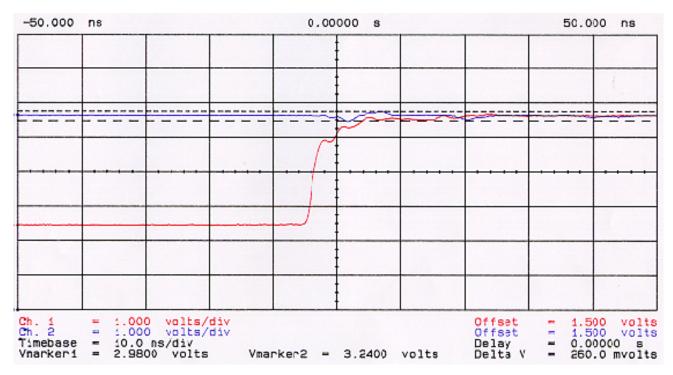

The ABT Widebus series (16-, 18-, and 20-bit functions) are offered in an SSOP package (see *Packaging* in this document), which TI developed to save valuable board space and reduce simultaneous switching effects. One might expect an increase in noise with 16 outputs switching in a single package; however, the simultaneous switching performance is actually improved. There is a GND pin for every two outputs and a  $V_{CC}$  pin for every four. This allows the transient current to be distributed across multiple power pins and decreases the overall  $d_i/d_t$  effect. This results in a typical  $V_{OLP}$  value on the order of 500 mV for the ABT16500, as shown in Figure 19.

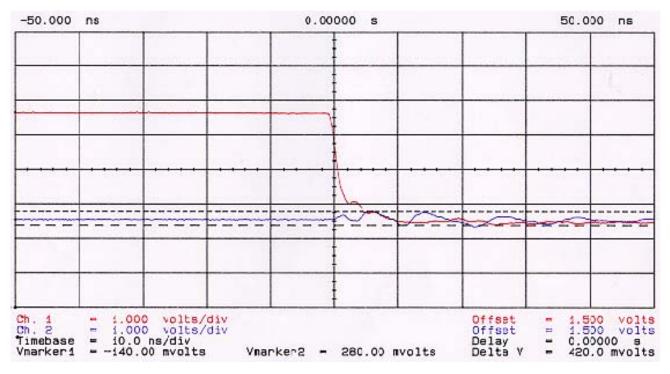

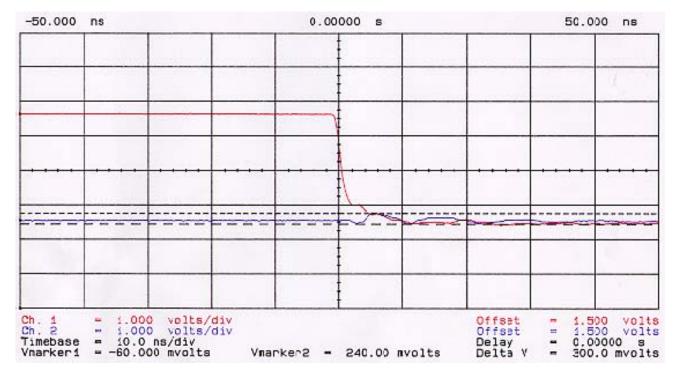

Figure 18. ABT646A Simultaneous-Switching Waveform

Figure 19. ABT16500B Simultaneous-Switching Waveform

#### **Advanced Packaging**

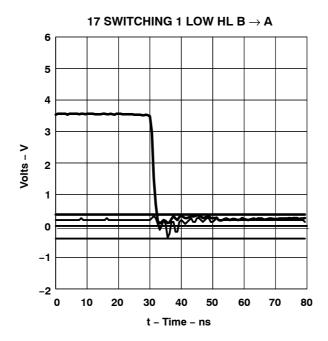

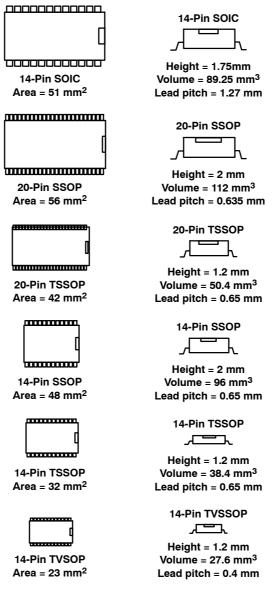

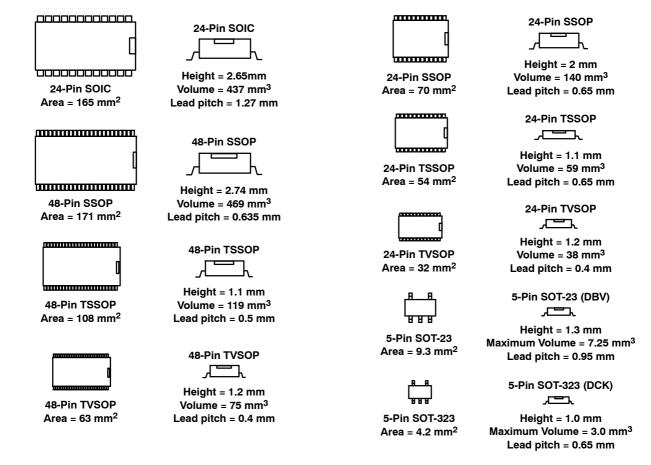

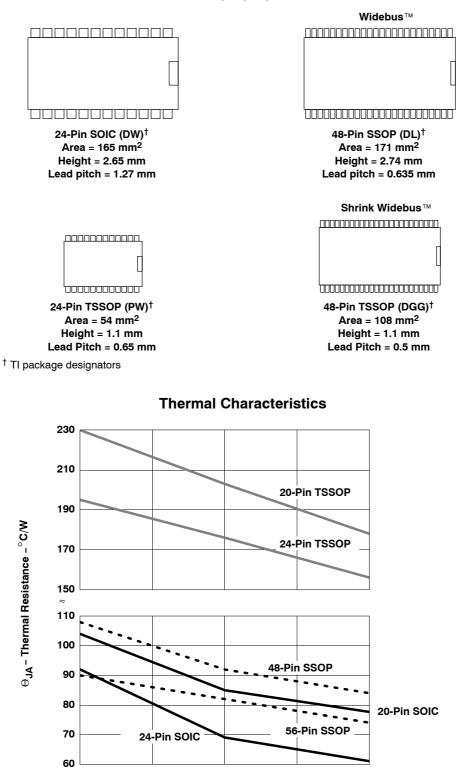

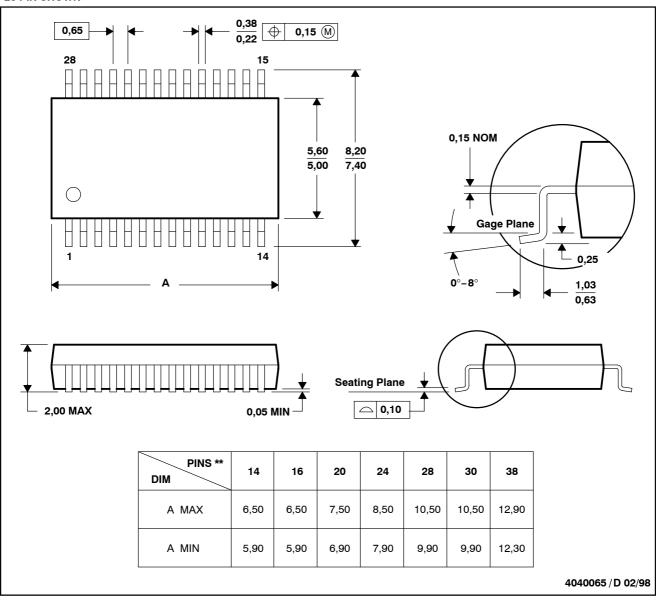

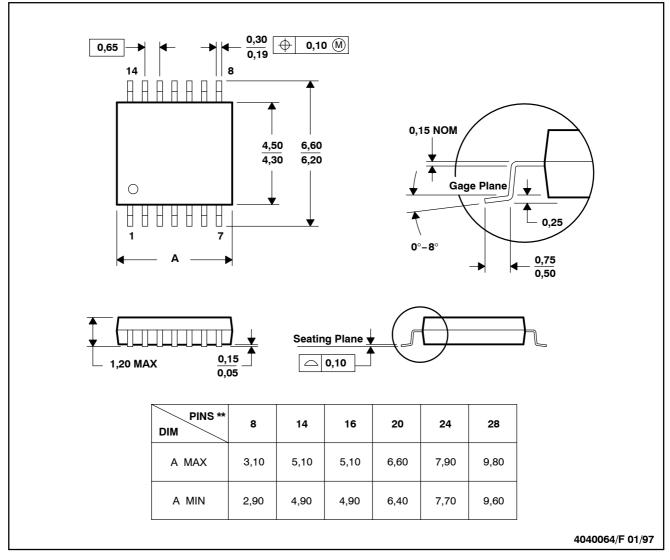

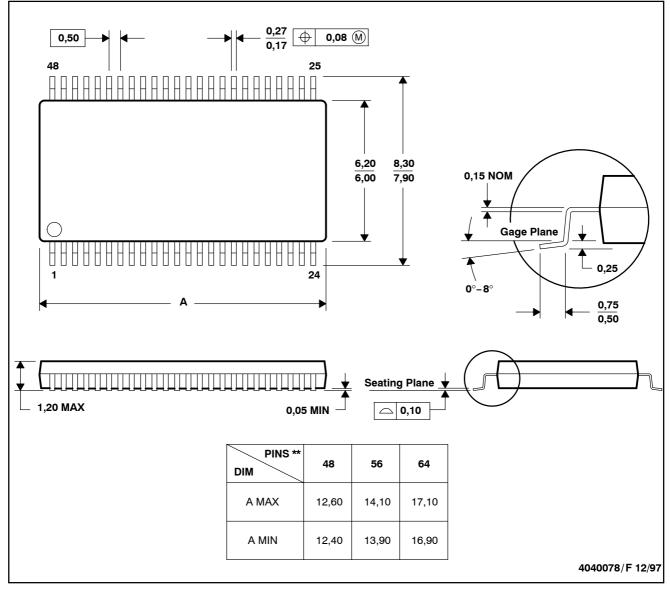

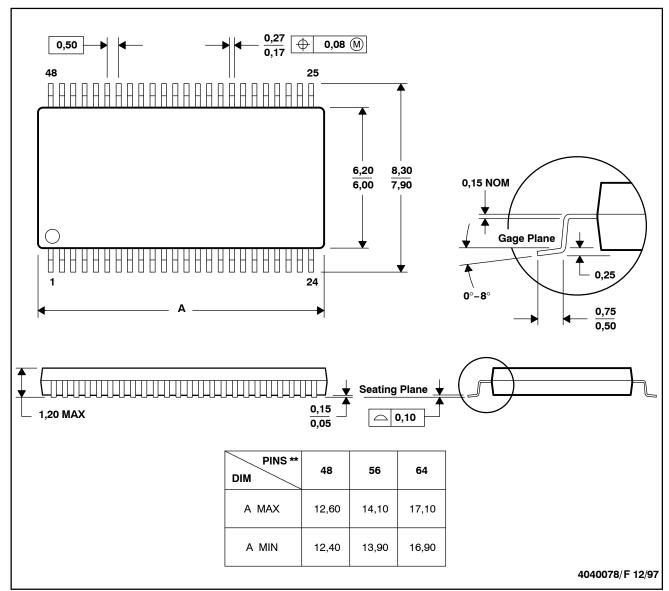

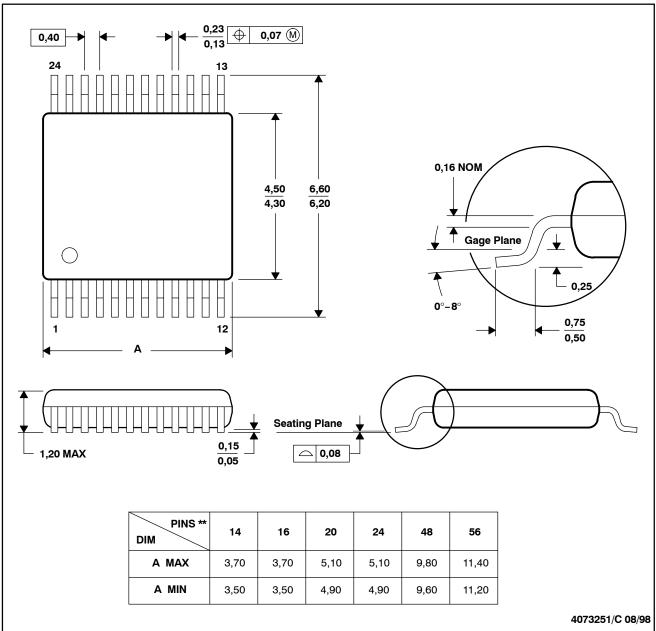

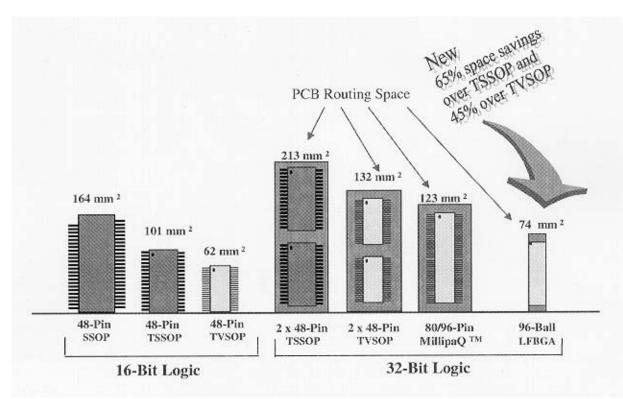

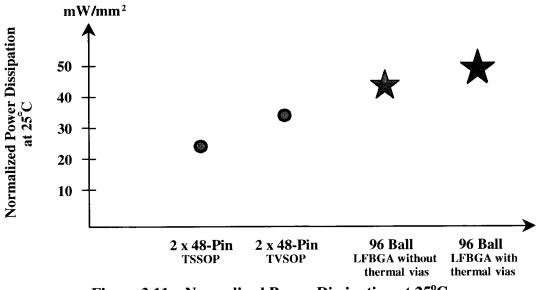

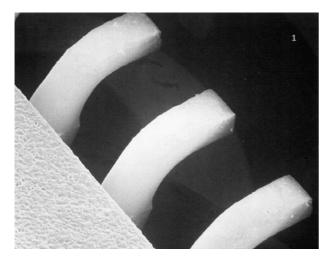

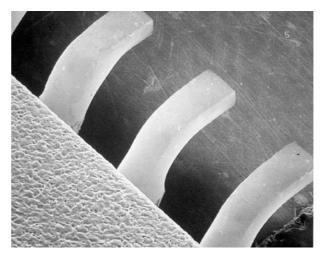

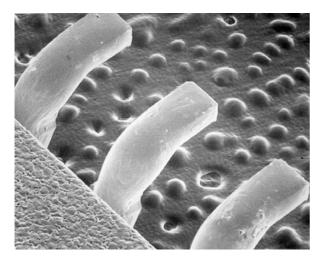

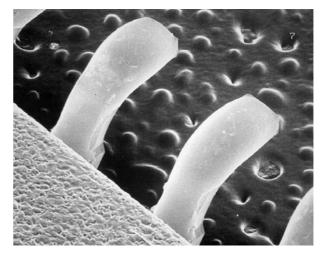

Along with a strong commitment to provide fast, low- power, high-drive ICs, TI is the leader in logic packaging advancements. The development of the shrink small-outline package (SSOP) in 1989 provided system designers the opportunity to reduce the amount of board space required for bus-interface devices by 50%. Several 24-pin solutions including the familiar SOIC, the SSOP, and the TSOP (thin small-outline package) are shown in Figure 20.

Figure 20. 24-Pin Surface-Mount Comparison

The 48/56-pin SSOP packages allow for twice the functionality (16-, 18-, and 20-bit functions) in approximately the same board area as a standard SOIC. This is accomplished by using a 25-mil (0.635 mm) lead pitch, as opposed to 50-mil (1.27 mm) in SOIC. Figure 21 shows a typical pinout structure for the 48-pin SSOP. The flow-through architecture is standard for all Widebus devices, making signal routing easier during board layout. Also note the distributed GND and V<sub>CC</sub> pins, which improve simultaneous switching effects as discussed in *Signal Integrity* in this document.

|          |             | í I               |    | _       |                   |              |

|----------|-------------|-------------------|----|---------|-------------------|--------------|

| 1        |             | 10E [             | 1  | ر<br>48 | ] 2 <u>0E</u>     | 7            |

| 16 Bit < |             | 1Y1 [             | 2  | 47      | ] 1A1             |              |

|          |             | 1Y2 [             | 3  | 46      | ] 1A2             |              |

|          |             | GND [             | 4  | 45      | ] GND             |              |

|          | Eight Bit < | 1Y3 [             | 5  | 44      | ] 1A3             |              |

|          |             | 1Y4 [             |    |         | ] 1A4             | Ļ            |

|          |             | V <sub>CC</sub> [ |    | 42      | ] v <sub>cc</sub> | ſ            |

|          |             | 2Y1 [             | 8  | 41      | 2A1               |              |

|          |             | 2Y2 [             | 9  | 40      | ] 2A2             |              |

|          |             | GND [             | 10 | 39      | ] GND             |              |

|          |             | 2Y3 [             | 11 | 38      | ] 2A3             |              |

|          |             | 🗸 2Y4 🛛           | 12 | 37      | ] 2A4             |              |

|          |             | 🦯 3Y1 🛛           | 13 | 36      | ] 3A1             | $\mathbf{b}$ |

|          | Eight Bit < | 3Y2 [             | 14 | 35      | ] 3A2             |              |

|          |             | GND [             | 15 |         | GND               |              |

|          |             | 3Y3 [             |    | 33      | 3A3               |              |

|          |             | 3Y4 [             | 17 |         | 3A4               |              |

|          |             | V <sub>CC</sub>   | 18 |         | V <sub>cc</sub>   | Į            |

|          |             | 4Y1 [             |    |         | 4A1               | ſ            |

|          |             | 4Y2 [             |    |         | 4A2               |              |

|          |             | GND 🛛             |    |         | GND               |              |

|          |             | 4Y3 [             |    |         | 4A3               |              |

|          |             | 4Y4 [             |    |         | 4A4               |              |

|          |             | 4 <u>0</u> E [    | 24 | 25      | 30E               | )            |

|          |             |                   |    |         |                   |              |

Figure 21. Distributed Pinout of 'ABT16244A

When using the small pin count SSOPs (8-, 9-, and 10-bit functions) the same functionality occupies less than half the board area of a SOIC (70 mm<sup>2</sup> vs 165 mm<sup>2</sup>). There also is a height improvement over the SOIC, which is beneficial when the spacing between boards is a consideration. For very dense memory arrays the packaging evolution has been taken one step further with the TSOP. The TSOP thickness of 1.1 mm gives a 58% height improvement over the SOIC.

Table 4 provides a quick reference of the mechanical specifications of the various SSOP packages. For more information, see *Recent Advancements in Bus-Interface Packaging and Processing*, literature number SCZA001A, and *Thin Very Small-Outline Package (TVSOP)*, literature number SCBA009C.

| PACKAGE SPECIFICATIONS |      |                      |                   |                       |                                         | PIN SPECIFICATIONS   |                      |

|------------------------|------|----------------------|-------------------|-----------------------|-----------------------------------------|----------------------|----------------------|

| PACKAGE<br>TYPE        | PINS | INDUSTRY<br>STANDARD | THICKNESS<br>(mm) | BODY<br>WIDTH<br>(mm) | STANDOFF<br>HEIGHT<br>(mm) <sup>‡</sup> | PIN<br>PITCH<br>(mm) | PIN<br>WIDTH<br>(mm) |

| SSOP                   | 20   | EIAJ                 | 2.00              | 5.3                   | 0.05                                    | 0.650                | 0.30                 |

| SSOP                   | 24   | EIAJ                 | 2.00              | 5.3                   | 0.05                                    | 0.650                | 0.30                 |

| SSOP                   | 28   | JEDEC                | 2.59              | 7.5                   | 0.20                                    | 0.635                | 0.25                 |

| SSOP                   | 48   | JEDEC                | 2.59              | 7.5                   | 0.20                                    | 0.635                | 0.25                 |

| SSOP                   | 56   | JEDEC                | 2.59              | 7.5                   | 0.20                                    | 0.635                | 0.25                 |

| Table 4. | SSOP | Metric S | Specifications <sup>†</sup> |

|----------|------|----------|-----------------------------|

|----------|------|----------|-----------------------------|

<sup>†</sup> All values are maximum typical values unless otherwise indicated.

<sup>‡</sup> Minimum values

APPENDIX A 'ABT646A Characterization Data A

## SN54AB76826944866640H4R4CIERZAIONDAZA

# SN54AB76828944866640H4RACIERZAIONDAVA

## SN54AB75269744B166640H4PACIEPZAIONDATA

# SN54ABTHSEEMABIGGACHARACTEREATIONDATA

## SN54ABTERENTABIGGACHARACTERZATONDATA

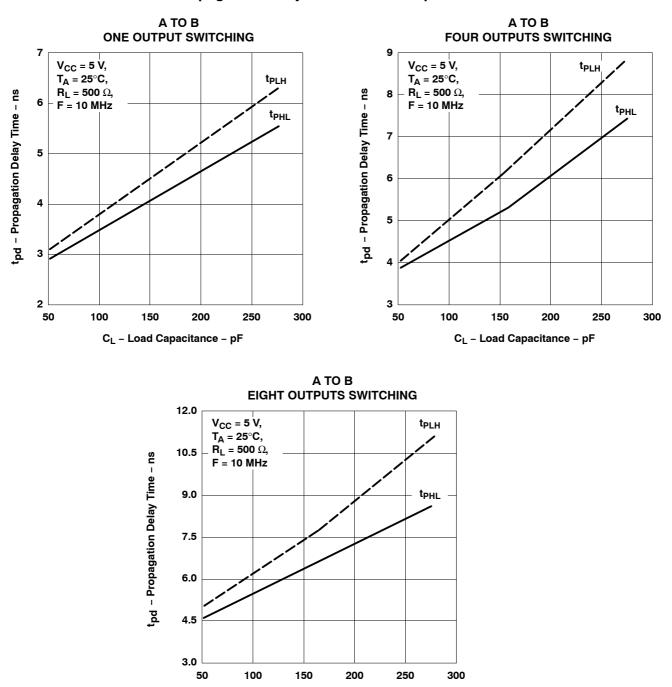

Propagation Delay Time vs Number of Outputs Switching

# SN54ABTHSEE MABIGEACHARACTEREATIONDATA

**Propagation Delay Time vs Load Capacitance**

C<sub>L</sub> – Load Capacitance – pF

## SN54ABTHERE IN ABIGE ACHARACIERZAIONDATA

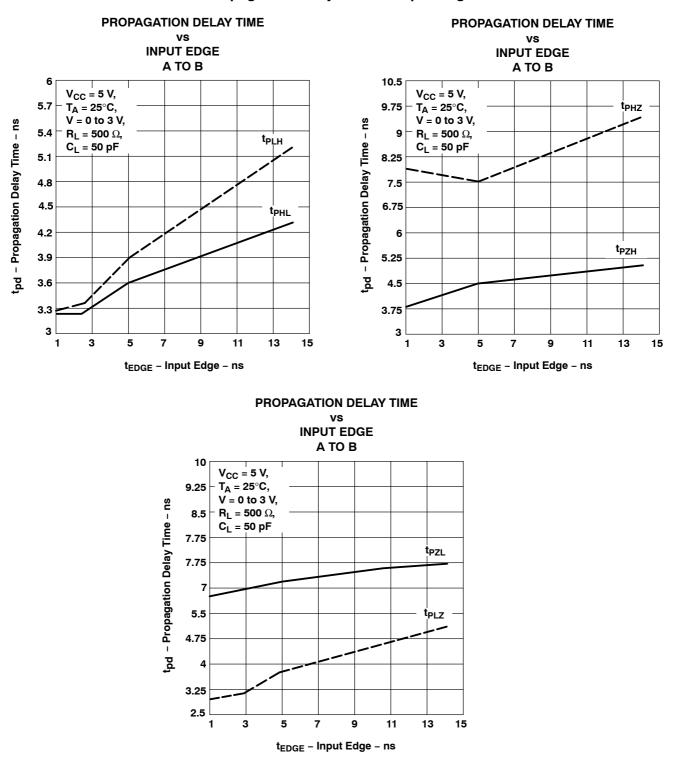

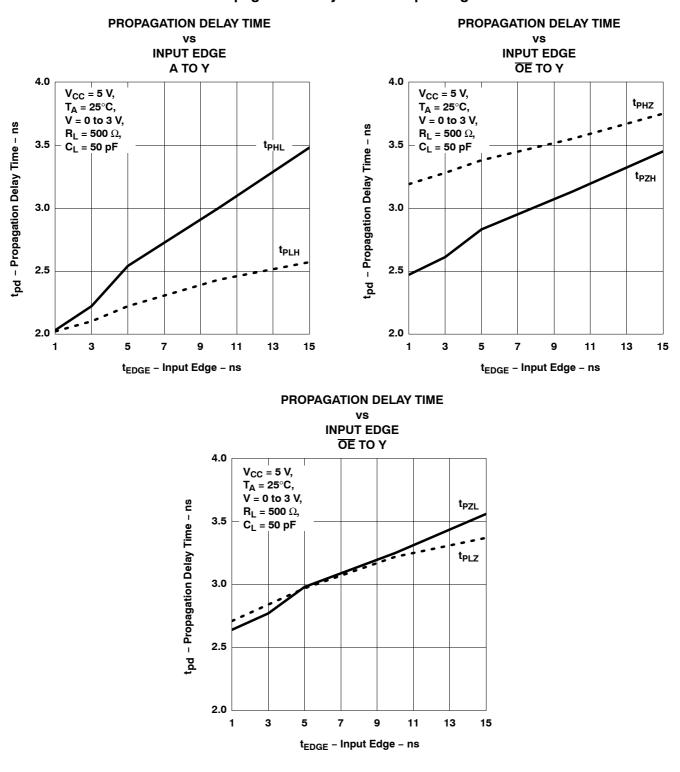

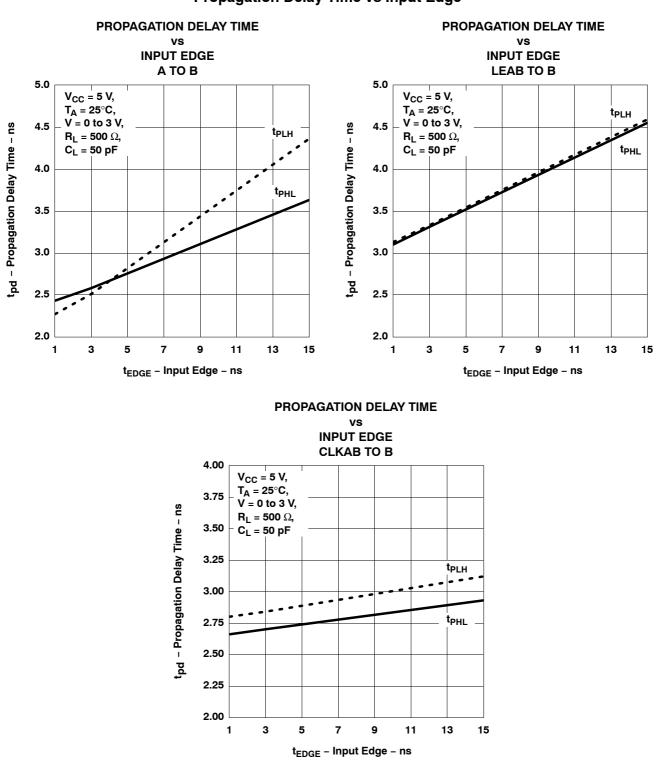

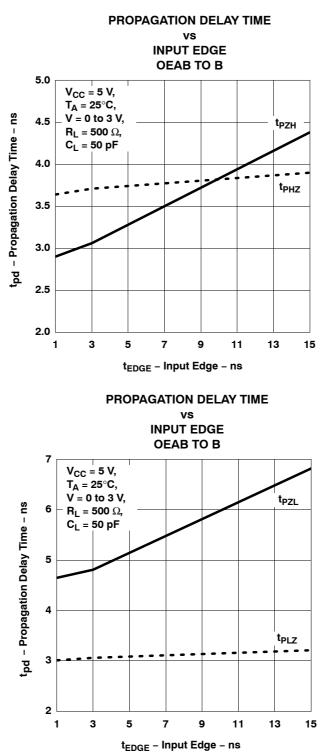

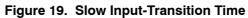

## **Propagation Delay Time vs Input Edge**

# SN54ABTHSTANKABIGGACHARACTERIZATIONDATA

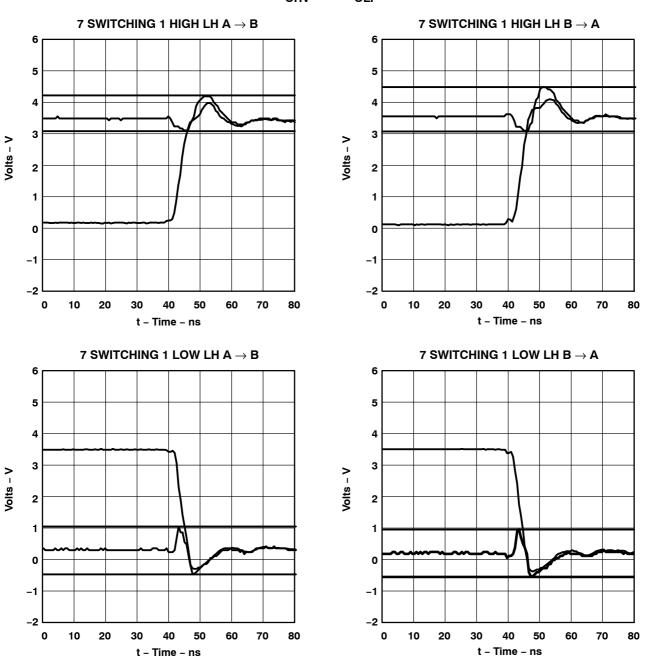

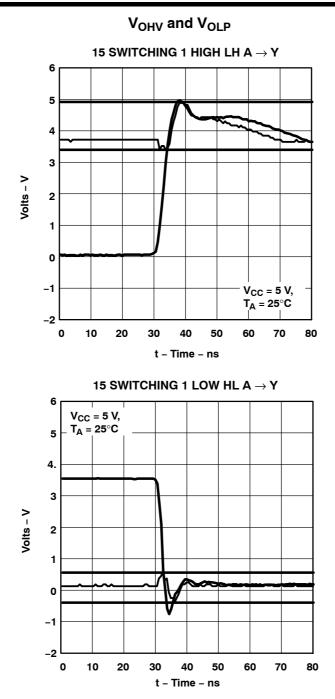

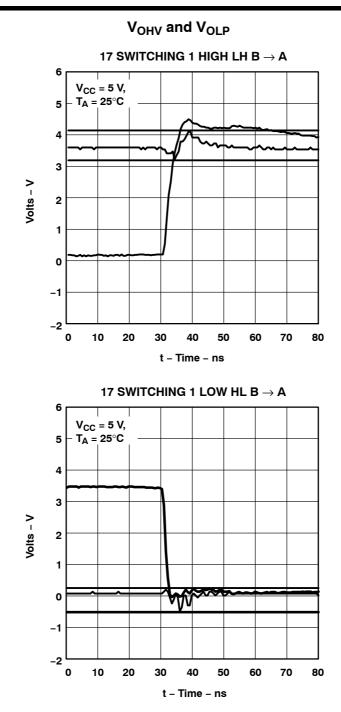

V<sub>OHV</sub> and V<sub>OLP</sub>

$V_{OHV}$  = Minimum (valley) voltage induced on a quiescent high-level output during switching of other outputs.  $V_{OLP}$  = Maximum (peak) voltage induced on a quiescent low-level output during switching of other outputs.

# SN54AB765269740B76640H2R4C1EH2A10NDAIA

# SN54AB75269749B166640H4PACIEFIZAIONDAVA

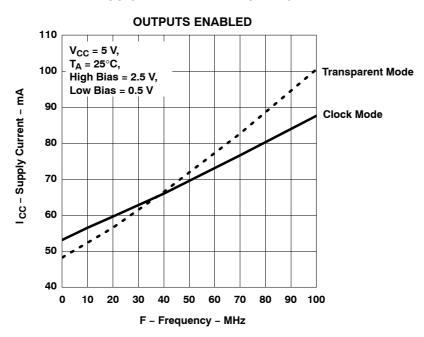

**Supply Current vs Frequency**

## APPENDIX B SN54ABT16244, SN74ABT16244A Characterization Data

B

### SN54ABTAN59474BI16244ACHARACIERZAIONDAVA

#### **Propagation Delay Time vs Temperature**

### SN54ABTAN52474BI16244ACHARACTERIZATIONDATA

**Propagation Delay Time vs Temperature**

### SN54ABTANGERAABTIG27/ACHARACTERZATONDATA

Propagation Delay Time vs Number of Outputs Switching

### SN54ABTAN52444BT6244ACHARACTERIZATIONDATA

**Propagation Delay Time vs Load Capacitance**

### SN54ABTAN52442BT6244ACHARACTERZATIONDATA

**Propagation Delay Time vs Input Edge**

### SN54ABTAN52444BI162444CH4PACTERIZATIONDATA

$V_{OHV}$  = Minimum (valley) voltage induced on a quiescent high-level output during switching of other outputs.  $V_{OLP}$  = Maximum (peak) voltage induced on a quiescent low-level output during switching of other outputs.

### SN54ABTAN52444BI162444CH4RACIERZAIONDAUA

### SN54ABTAN52444BI16244ACHARACIERZAIONDAVA

#### **Supply Current vs Frequency**

APPENDIX C

С

'ABT16500B Characterization Data

### SN54ABT #666999981980080-ARACIERZAIONDATA

#### **Propagation Delay Time vs Temperature**

### SN54ABT #6899988160080HARACIEHZAIONDAIA

### SN54ABT AGEONGETIGWECHARACTERIZATIONDATA

#### **Propagation Delay Time vs Temperature**

### SN54ABT #666999861160080HARACIEHZAIONDAIA

### SN54ABT 1666991981160080-14RACIERZAIONDAIA

#### **Propagation Delay Time vs Load Capacitance**

### SN54ABT #68999881160080HARACIEHZAIONDAVA

**Propagation Delay Time vs Input Edge**

### SN54ABT #65599#68080HARACIERZAIONDAVA

Propagation Delay Time vs Input Edge

### SN54ABT #66699968160080HARACIEHZAIONDAJA

$V_{OHV}$  = Minimum (valley) voltage induced on a quiescent high-level output during switching of other outputs.  $V_{OLP}$  = Maximum (peak) voltage induced on a quiescent low-level output during switching of other outputs.

### SN54ABT #65599#650160080HARACIEHZAIONDAIA

### SN54ABT #66699988160080-ARACIERZAIONDAVA

**Supply Current vs Frequency**

NOTE: Characteristics for latch mode are similar to those when in clock mode.

**Supply Current vs Frequency**

NOTE: Characteristics for latch mode are similar to those when in clock mode.

# Advanced High-Speed CMOS (AHC) Logic Family

SCAA034B January 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated

### Contents

| Title |

|-------|

|-------|

| Introduction                                                                                                                                                             | 1-65                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| High-Speed CMOS (HC) 1                                                                                                                                                   | 1-65                         |

| Advanced High-Speed CMOS (AHC) 1                                                                                                                                         | 1-66                         |

| Protection Circuitry                                                                                                                                                     | 1–66                         |

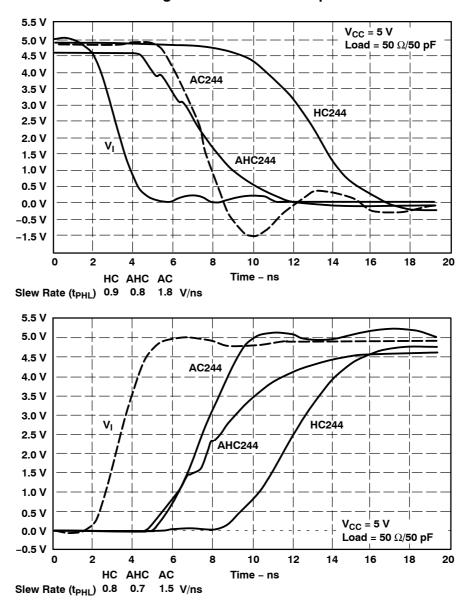

| Switching Characteristics 1                                                                                                                                              | 1-68                         |

| Power Considerations                                                                                                                                                     | 1-68                         |

| Power Dissipation                                                                                                                                                        | 1-69                         |

| Input Characteristics                                                                                                                                                    | 1-70                         |

| AHC Input Circuitry       1         Input Current Loading       1         Supply Current Change ( $\Delta I_{CC}$ )       1                                              | 1-72                         |

| DC Characteristics 1                                                                                                                                                     | 1-73                         |

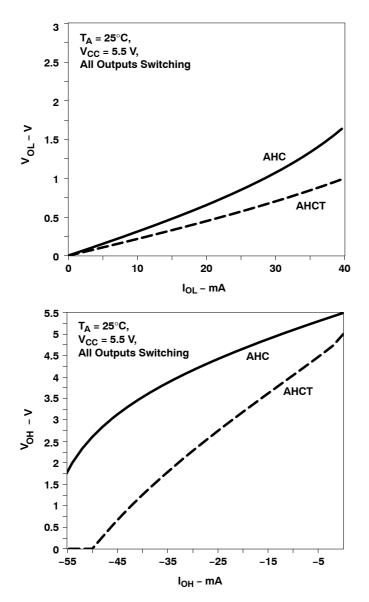

| AHC/AHCT Output Circuitry       1         Output Drive       1         Partial Power Down       1                                                                        | 1–74                         |

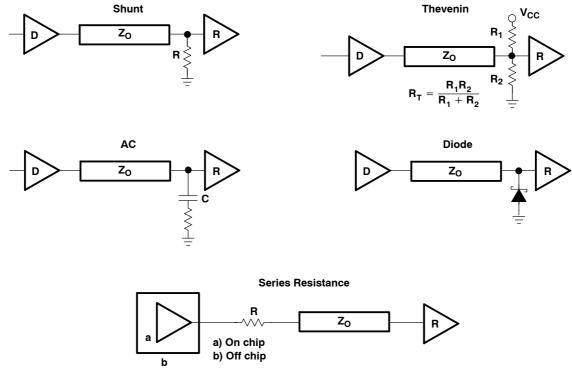

| Proper Termination of Outputs                                                                                                                                            | 1–75                         |

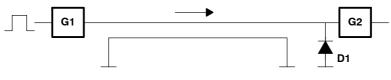

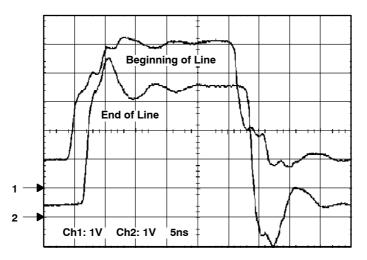

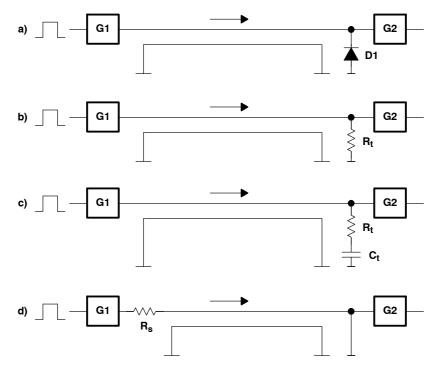

| Common Termination Techniques       1         Shunt       1         AC       1         Thevenin       1         Diode       1         Series (Source Terminated)       1 | 1–75<br>1–76<br>1–76<br>1–76 |

| Signal Integrity                                                                                                                                                         | 1–77                         |

| AHC Versus HC                                                                                                                                                            | 1-80                         |

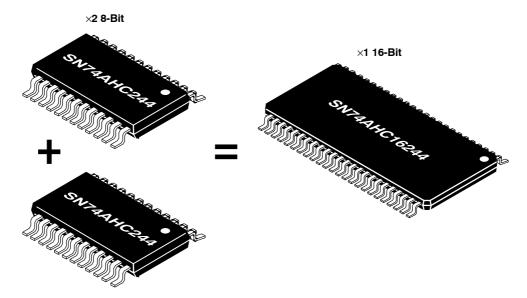

| Advanced Packaging 1                                                                                                                                                     | 1-81                         |

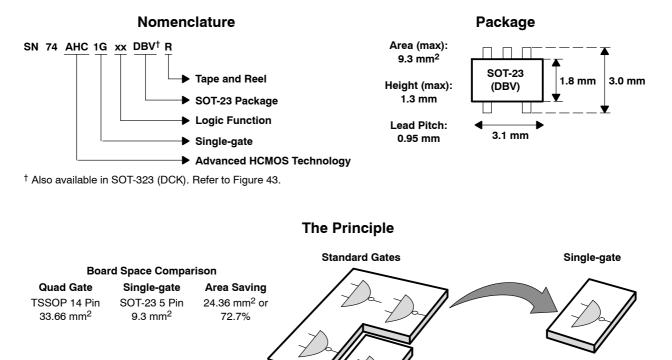

| Microgate Logic                                                                                                                                                          | 1-82                         |

| Acknowledgment                                                                                                                                                           |                              |

Page

### List of Illustrations

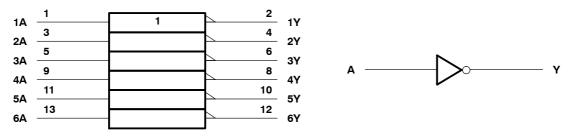

| Figure | Title                                                                     | Page |

|--------|---------------------------------------------------------------------------|------|

| 1      | ESD Input Protection Circuitry                                            | 1-66 |

| 2      | ESD Output Protection Circuitry                                           | 1–67 |

| 3      | Parasitic Bipolar Transistors in CMOS                                     | 1–67 |

| 4      | Schematic of Parasitic SCR Showing P-Gate and N-Gate Electrodes Connected | 1-68 |

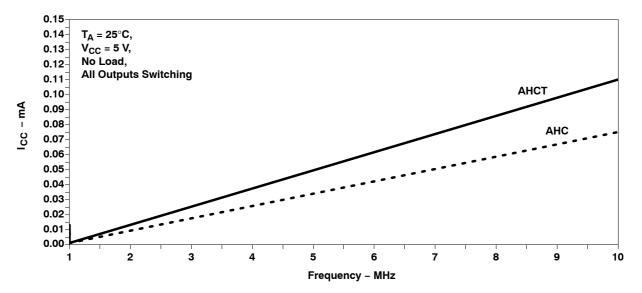

| 5      | I <sub>CC</sub> Versus Frequency                                          | 1–69 |

| 6      | Supply Current Versus Input Voltage                                       | 1-70 |

| 7      | Simplified Input Stage of an AHC Circuit                                  | 1-70 |

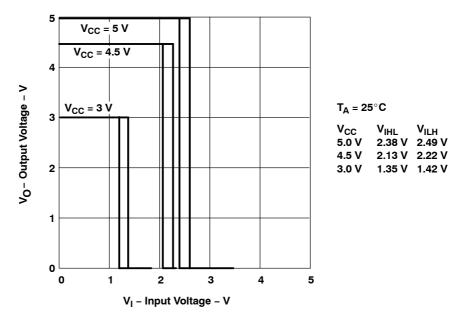

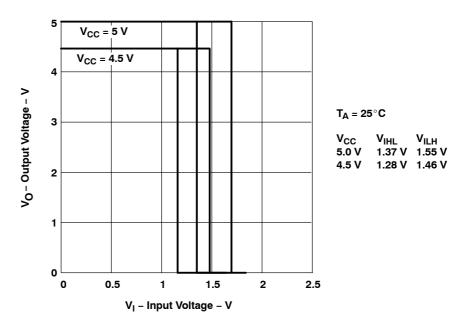

| 8      | Output Voltage Versus Input Voltage (AHC04)                               | 1–71 |

| 9      | Output Voltage Versus Input Voltage (AHCT04)                              | 1–71 |

| 10     | Input Current Versus Input Voltage (AHC245)                               | 1–72 |

| 11     | Simplified Output Stage of an AHC Circuit                                 | 1–73 |

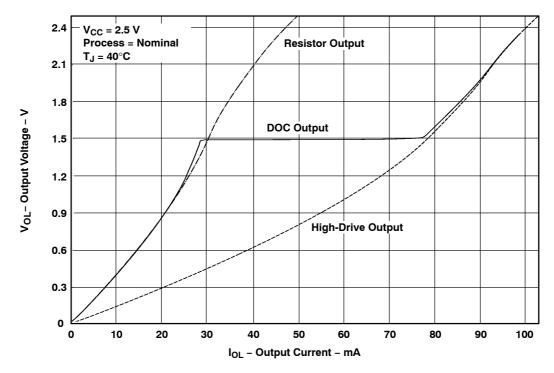

| 12     | AHC Output Characteristics                                                | 1–74 |

| 13     | Termination Techniques                                                    | 1–75 |

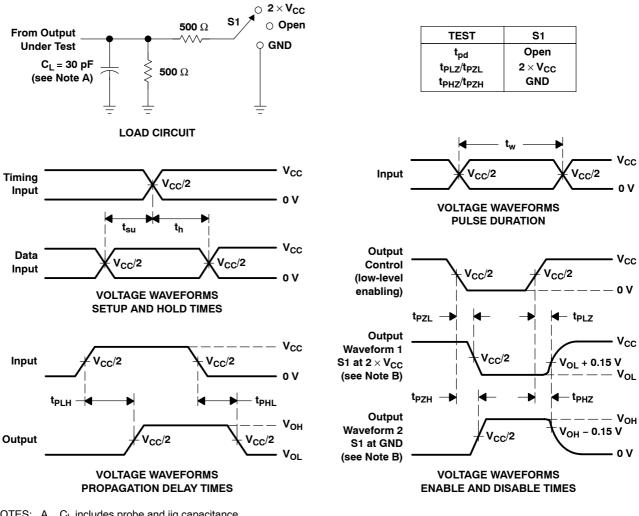

| 14     | Output Buffer With External Parasitics                                    | 1–78 |

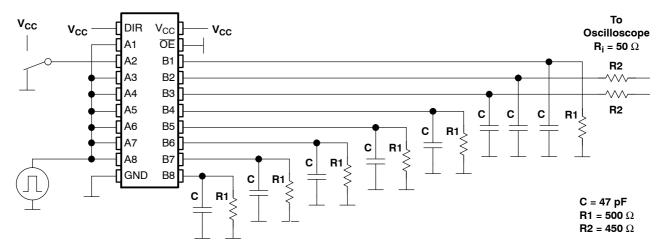

| 15     | Simultaneous-Switching-Noise Waveform                                     | 1–79 |

| 16     | Ground-Bounce Test Circuit                                                | 1–79 |

| 17     | AHC/AHCT and HC Family Positioning                                        | 1-80 |

| 18     | AHC Packages                                                              | 1-81 |

| 19     | SN74AHC245 Pinout                                                         | 1-82 |

| 20     | 5-Pin Microgate Logic Pinout                                              | 1-82 |

### List of Tables

| Table | Title                                              | Page |

|-------|----------------------------------------------------|------|

| 1     | HC and AHC Performance Comparison (Typical Values) | 1–68 |

| 2     | Input-Current Specification                        | 1-72 |

| 3     | ΔI <sub>CC</sub> -Current Specification            | 1-72 |

| 4     | AHC DC Specifications                              | 1-73 |

| 5     | Termination Techniques Summary                     | 1–77 |

| 6     | AHC and HC Features (Typical Values)               | 1-80 |

#### Introduction

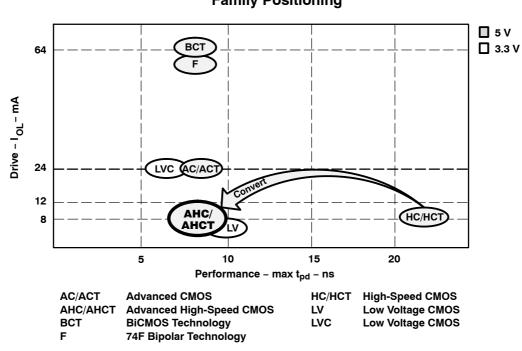

The Texas Instruments (TI<sup>™</sup>) advanced high-speed CMOS (AHC) logic family provides a natural migration for high-speed CMOS (HCMOS) users who need more speed for low-power, and low-drive applications. Unlike many other advanced logic families, AHC does not have the drawbacks that come with higher speed, e.g., higher signal noise and power consumption. The AHC logic family consists of gates, medium-scale integrated circuits, and octal functions fabricated using the EPIC<sup>™</sup> process that features higher performance than the HCMOS HC product family at comparable cost.

This application report introduces the AHC logic family characterization information to supplement the AHC/AHCT Logic Advanced High-Speed CMOS Data Book, literature number SCLD003A. The additional information is to aid design engineers in more accurately designing their digital logic systems. The focus is on the family's features and benefits, product characteristics, and design guidelines. This application report is divided into sections, each dealing with a specific characteristic of the AHC logic family. This application report focuses on the AHC logic family and compares it to the HC family.

The main topics discussed are:

- High-Speed CMOS (HC)

- Advanced High-Speed CMOS (AHC)

- Protection Circuitry

- AC Performance

- Power Considerations

- Input Characteristics

- Output Characteristics

- Signal Integrity

- AHC Versus HC

- Advanced Packaging

- Microgate Logic

For more information on TI's AHC logic products, please contact your local TI field sales office or an authorized distributor, or call TI at 1-800-336-5236.

#### High-Speed CMOS (HC)

HC has the following characteristics:

- The HC family covers a wide range of applications: low power drain for low-speed systems, and a slightly higher drain for higher-speed systems.

- The HC family has ac parameters ensured at supply voltages of 2 V, 4.5 V, and 6 V over the full operating temperature range into a 50-pF load. The TTL compatible version, HCT, is specified for a 4.5-V to 5.5-V V<sub>CC</sub> range.

- In HC, only the gates that are switching contribute to the dynamic system power. This reduces the size of the power supply required, thus providing lower system cost and higher reliability through lower heat dissipation.

- HC devices are ideal for battery-operated systems, or systems requiring battery backup because there is virtually no static power dissipation.

- Improved noise immunity is due to the rail-to-rail (V<sub>CC</sub>-to-ground) output voltage swings.

- HC devices are warranted for operation over an extended temperature range of -40°C to 85°C.

#### Advanced High-Speed CMOS (AHC)

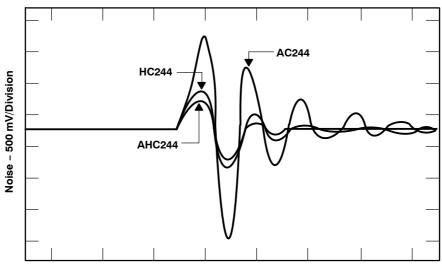

AHC can be used for higher-speed applications. Some advantages of using AHC over HC are:

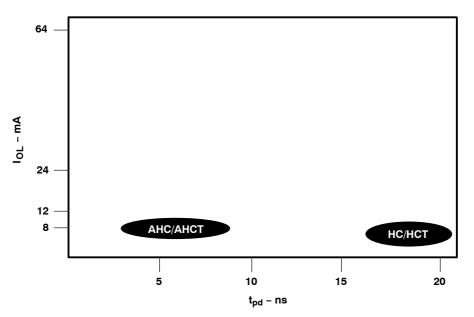

- The AHC logic family is almost three times faster than the HC family. The AHC logic family has a typical propagation delay of about 5.2 ns.

- The AHC logic family allows designers to combine the low-noise characteristics of HCMOS devices with today's performance levels without the overshoot/undershoot problems typical of higher-drive devices.

- The AHC family has lower power consumption than the HC family.

- The output drive is  $\pm 8$  mA at 5-V V<sub>CC</sub> and  $\pm 4$  mA at 3.3-V V<sub>CC</sub>.

- AHC devices are available in D and DW (SOIC), DB (SSOP), N (PDIP), PW (TSSOP), and DGV (TVSOP) packages. Selected AHC devices are available in military versions (SN54AHCxx).

- Microgate Logic (single-gate) versions that simplify routing are also available.

#### **Protection Circuitry**

Electrostatic discharge (ESD) and latchup are two traditional causes of CMOS device failure. To protect AHC devices from ESD and latchup, additional circuitry has been implemented at the inputs and outputs of each device.

#### **Electrostatic Discharge**

ESD occurs when a buildup of static charges on one surface arcs through a dielectric to another surface that has the opposite charge. The end effect is the ESD causes a short between the two surfaces. These damaged devices might pass normal data sheet tests, but eventually fail. The input and output protection circuitry designed by TI provides immunity to over 2000 V in the human-body-model test, over 200 V in the machine-model test, and over 1000 V in the charged-device model test.

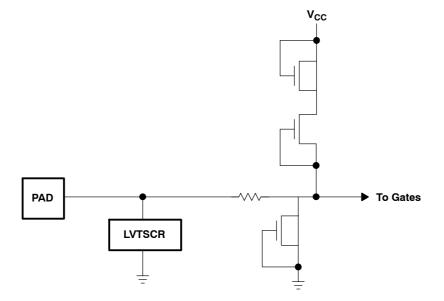

Figure 1 shows the circuitry implemented to provide protection for the input gates against ESD. The primary protection device is a low-voltage-triggered silicon-controlled rectifier (LVTSCR). During an ESD event, most of the current is diverted through the LVTSCR. Additional protection is provided by the resistor and secondary clamp transistors, which break down during an ESD event and protect the gate oxides.

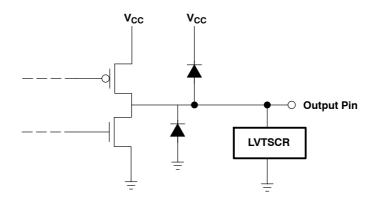

Figure 2 shows how the LVTSCR protects an output.

Figure 1. ESD Input Protection Circuitry

Figure 2. ESD Output Protection Circuitry

#### **Latchup Protection**

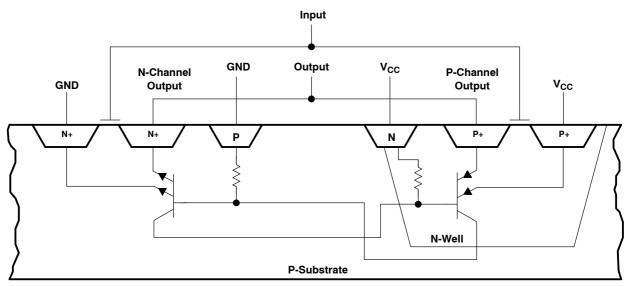

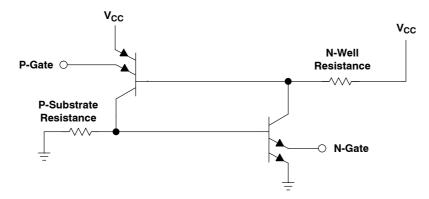

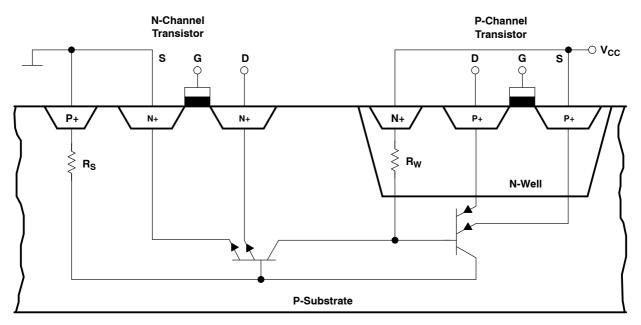

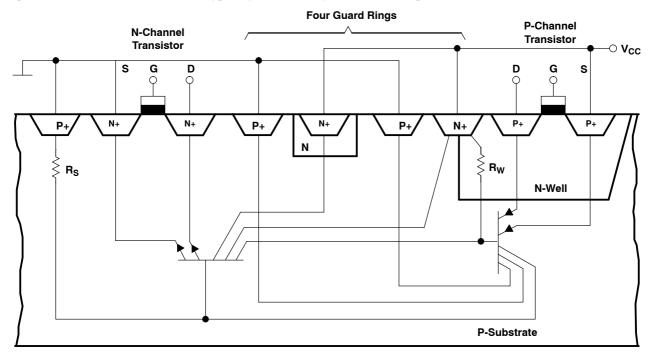

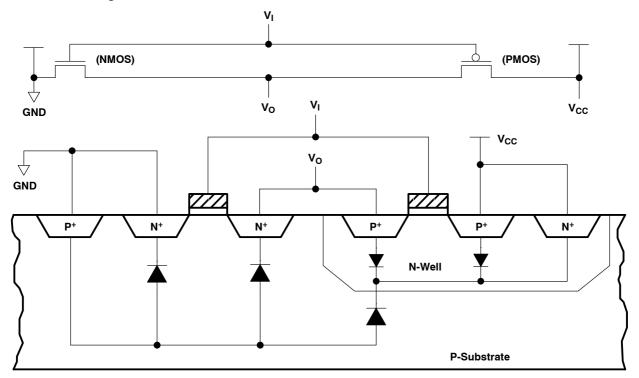

Internal to almost all CMOS devices are two parasitic bipolar transistors; one p-n-p and one n-p-n. Figure 3 shows the cross section of a typical CMOS inverter with the parasitic bipolar transistors. As shown in Figure 4, these parasitic bipolar transistors are naturally configured as a thyristor or a silicon-controlled rectifier (SCR). These transistors conduct when one or more of the p-n junctions become forward biased. When this happens, each parasitic transistor supplies the necessary base current for the other to remain in saturation. This is known as the latchup condition and could destroy the device if the supply current is not limited.

Figure 3. Parasitic Bipolar Transistors in CMOS

#### Figure 4. Schematic of Parasitic SCR Showing P-Gate and N-Gate Electrodes Connected

A conventional thyristor is fired (turned on) by applying a voltage to the base of the n-p-n transistor, but the parasitic CMOS thyristor is fired by applying a voltage to the emitter of either transistor. One emitter of the p-n-p transistor is connected to an emitter of the n-p-n transistor, which is also the output of the CMOS gate. The other two emitters of the p-n-p and the n-p-n transistors are connected to  $V_{CC}$  and ground, respectively. Therefore, to trigger the thyristor there must be a voltage greater than  $V_{CC} + 0.5$  V or less than -0.5 V and there has to be sufficient current to cause the latchup condition.

Latchup cannot be completely eliminated. The alternative is to prevent the thyristor from triggering. TI has improved the circuit design by adding an additional diffusion or guard ring. The guard ring provides isolation between the device pins and any p-n junction that is not isolated by any transistor gate.

#### **Switching Characteristics**

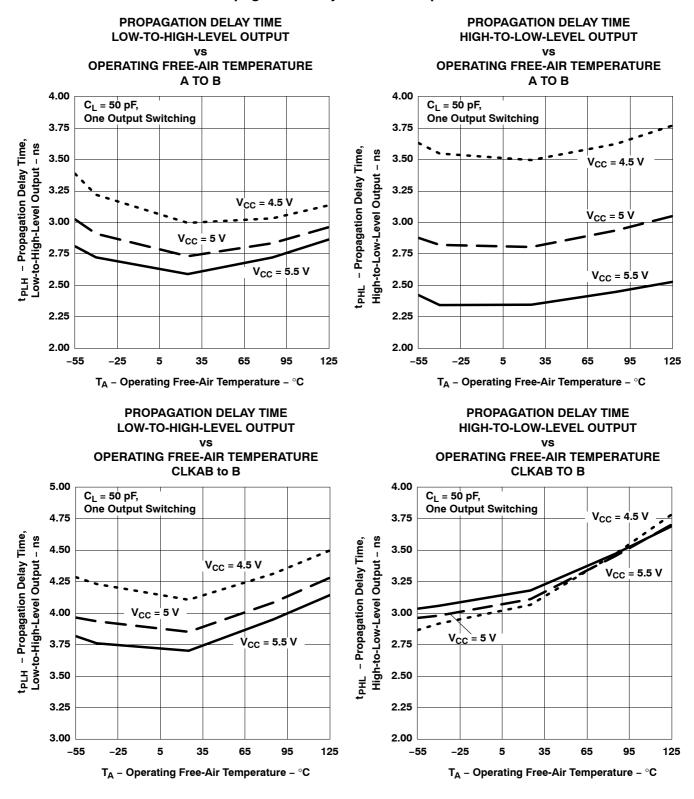

The switching characteristics of the AHC are similar to those of the AHCT in terms of the operating conditions and limits, except for the AHCT input TTL compatibility. Table 1 gives the performance figures for the HC/HCT and the AHC/AHCT logic parts. Individual data sheets provide parameter values for the AHC and the AHCT devices for different values of operating free-air temperature, number of outputs switching, and load capacitance.

| DEVICE          | SN74HC | SN74HCT | SN74AHC | SN74AHCT |

|-----------------|--------|---------|---------|----------|

| 244 buffer      | 13 ns  | 15 ns   | 5.8 ns  | 5.4 ns   |

| 245 transceiver | 15 ns  | 14 ns   | 5.8 ns  | 4.5 ns   |

| 373 latch       | 15 ns  | 20 ns   | 5 ns    | 5 ns     |

| 374 flip-flop   | 17 ns  | 25 ns   | 5.4 ns  | 5 ns     |

Table 1. HC and AHC Performance Comparison (Typical Values)

AHC is almost three times faster than HC.

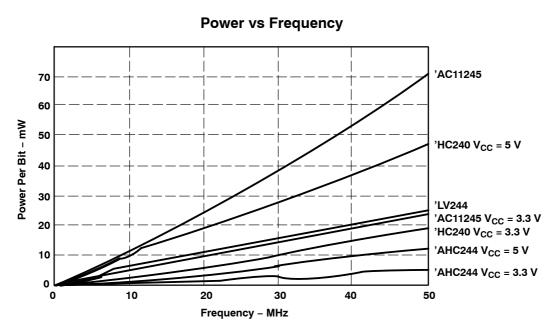

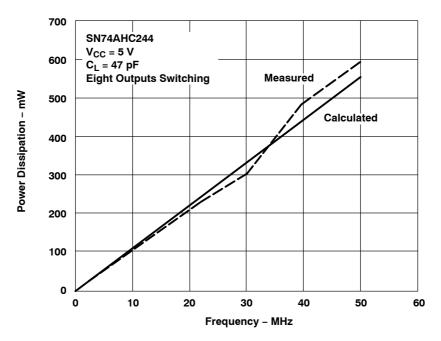

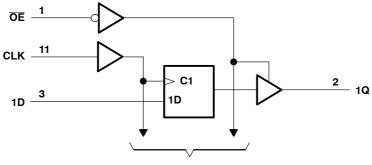

#### **Power Considerations**

The power dissipation of CMOS devices can be divided into three components:

- Quiescent power dissipation, Pq

- Transient power dissipation, Pt

- Capacitive power dissipation, P<sub>c</sub>

The quiescent power is the product of  $V_{CC}$  and the quiescent current,  $I_{CC}$ . The quiescent current is the reverse current through the diodes that are reverse biased. This reverse current is generally very small (a few nA), which makes the quiescent power insignificant. However, for circuits that are in static condition for long periods, the quiescent power must be considered.

The transient power is due to the current that flows only when the transistors are switching from one logic level to the other. During this time, both of the transistors are partially on, which produces a low-impedance path between  $V_{CC}$  and ground that results in a current spike. The rise (or fall) time of the input signal has a direct effect on the duration of the current spike. This is because the faster the input signal passes through the transistors, the less time both transistors are partially on. The transient power is dependent on the characteristics of the transistors, the switching frequency, and the rise and fall times of the input signal. The component can be calculated using the following equation:

$$\mathbf{P}_{t} = \mathbf{C}_{pd} \times \mathbf{V}_{CC}^{2} \times \mathbf{f}_{I} \tag{1}$$

Where:

$\begin{array}{lll} V_{CC} &= & Supply \ voltage \ (V) \\ f_{I} &= & Input \ frequency \ (Hz) \\ C_{pd} &= & Power \ dissipation \ capacitance \ (F) \end{array}$

Additional capacitive power dissipation is caused by the charging and discharging of external load capacitance and is dependent on the switching frequency. To calculate the power, the following equation can be used:

$$\mathbf{P}_{\mathrm{C}} = \mathbf{C}_{\mathrm{L}} \times \mathbf{V}_{\mathrm{CC}}^{2} \times \mathbf{f}_{\mathrm{O}}$$

(2)

Where:

$V_{CC}$  = Supply voltage (V)  $f_{O}$  = Output frequency (Hz)  $C_{L}$  = External load capacitance (F)

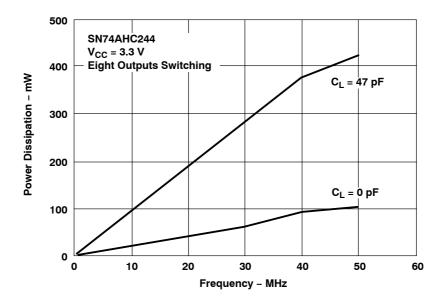

#### **Power Dissipation**

AHCT devices are used primarily to interface TTL output signals to CMOS inputs. To make the inputs of the AHCT devices TTL-voltage compatible, the input transistor geometries were changed. This increased the power consumption, as compared to the equivalent AHC device, if the input is kept at a level other than GND or  $V_{CC}$ . The increase in power consumption occurs because TTL input levels cause both transistors in the transistor pair to be partially turned on. Included in the tables for the AHCT devices is the parameter  $\Delta I_{CC}$ , which enables the designer to compute how much additional current the AHCT device draws per input when at a TTL-voltage level.

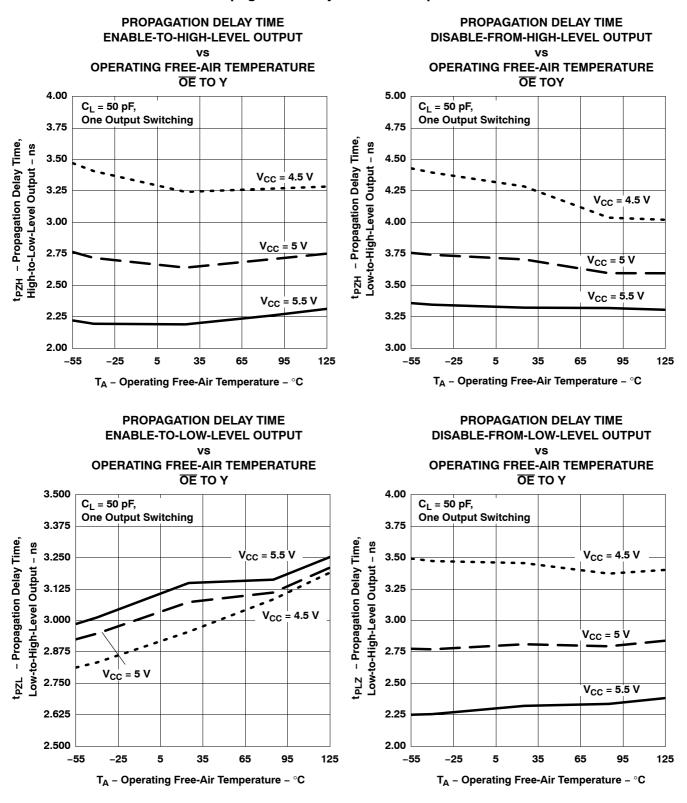

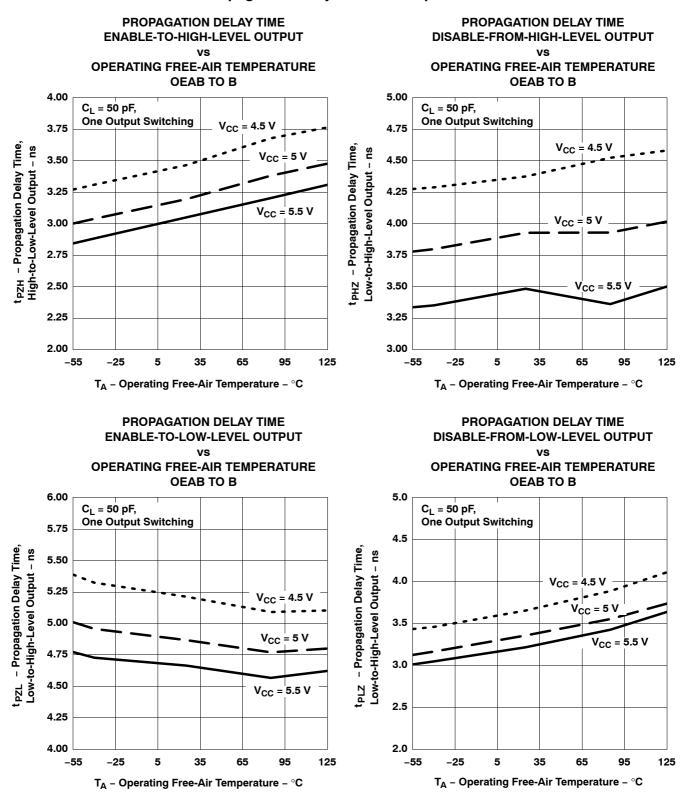

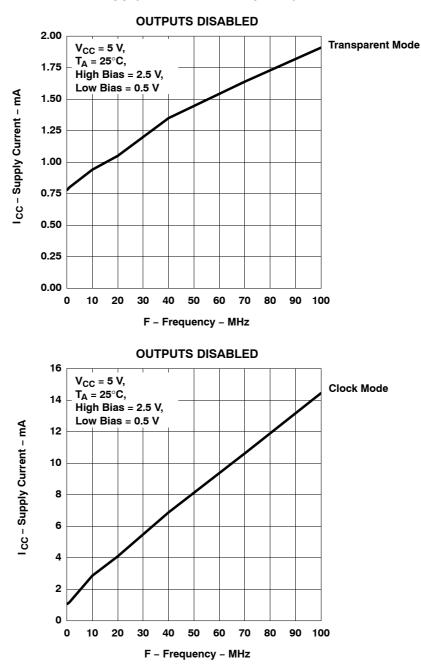

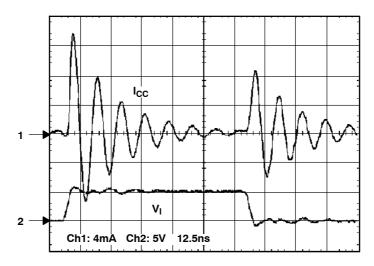

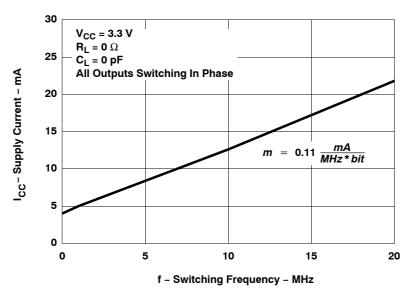

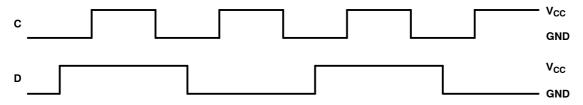

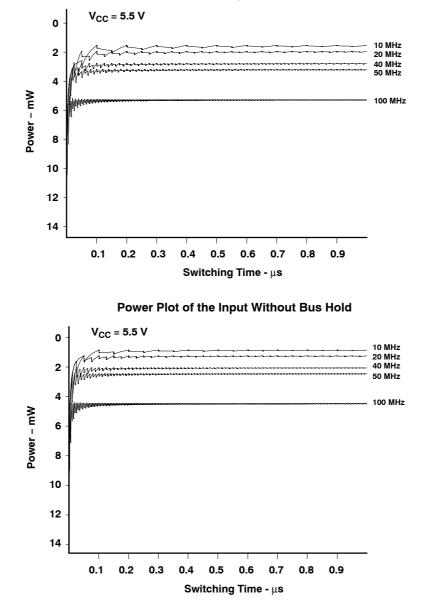

Figure 5 shows the relation between the supply current and the frequency of operation for the AHC245 and the AHCT245. The increase in power consumption for the AHCT is relatively insignificant.

Figure 5. I<sub>CC</sub> Versus Frequency

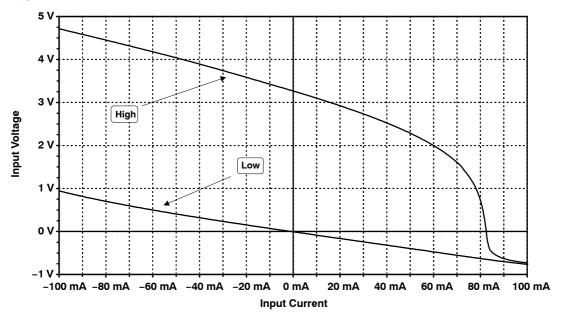

#### **Input Characteristics**

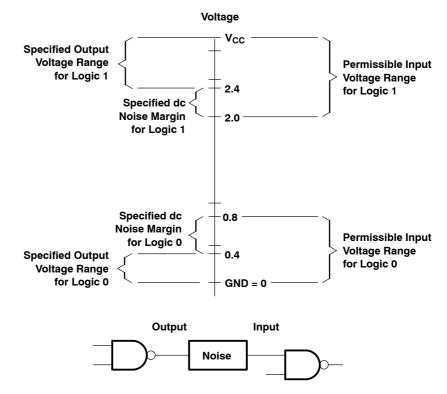

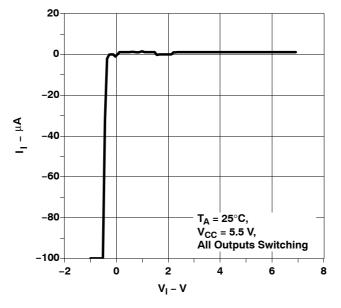

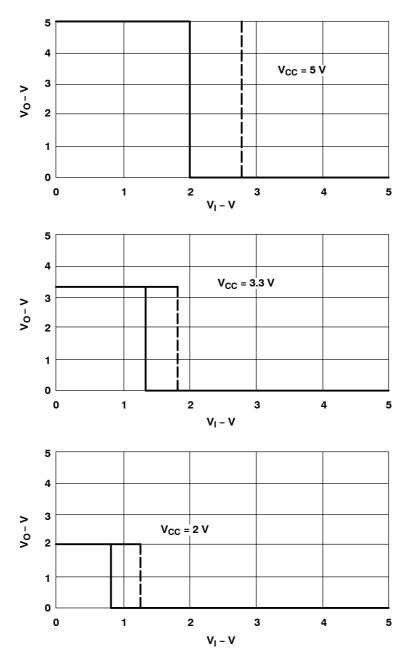

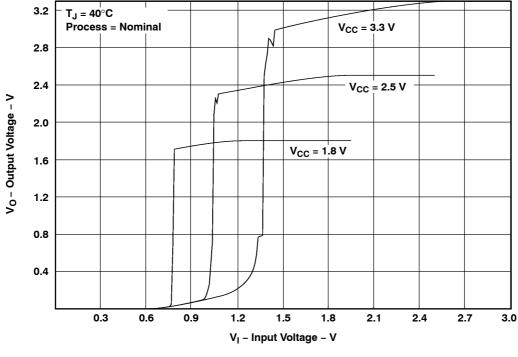

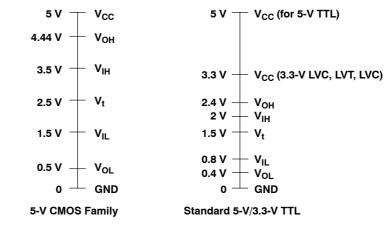

The AHC logic family input structure is such that the 5-V CMOS dc  $V_{IL}$  and  $V_{IH}$  fixed levels of 1.5 V and 3.5 V are ensured, meaning that, while the threshold voltage of 2.5 V is typically where the transition from a recognized low input to a recognized high input occurs, it is at 1.5 V and 3.5 V that the corresponding output levels are specified. For AHCT,  $V_{IL}$  and  $V_{IH}$  fixed levels of 0.8 V and 2 V are ensured, and the threshold voltage is 1.5 V. Figure 6 shows the characteristics for the AHC245 and the AHCT245.

Figure 6. Supply Current Versus Input Voltage

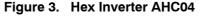

#### **AHC Input Circuitry**

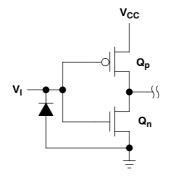

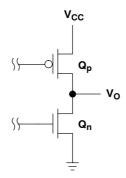

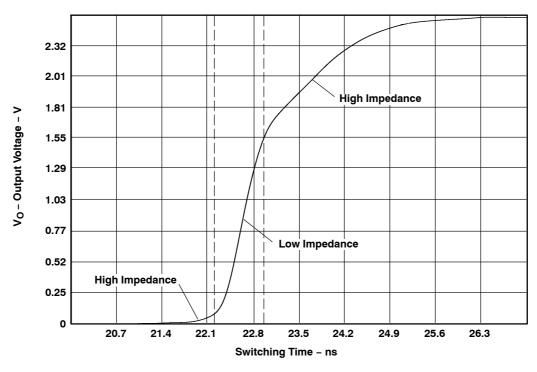

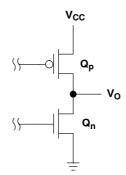

The simplified AHC input circuit shown in Figure 7 consists of two transistors, sized to achieve a threshold voltage of 2.5 V. Since  $V_{CC}$  is 5 V and the threshold voltage is commonly set to be centered around one-half of  $V_{CC}$  in a pure CMOS input, additional circuitry to reduce the voltage level is not required and the resulting simplified input structure consists of two transistors. When the input voltage  $V_I$  is low, the PMOS transistor ( $Q_p$ ) turns on and the NMOS transistor ( $Q_n$ ) turns off, causing current to flow through  $Q_p$ , resulting in the output voltage (of the input stage) to be pulled high. Conversely, when  $V_I$  is high,  $Q_n$  turns on and  $Q_p$  turns off, causing current to flow through  $Q_n$ , resulting in the output voltage (on the input stage) to be pulled low.

Figure 7. Simplified Input Stage of an AHC Circuit

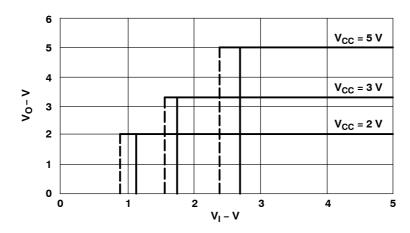

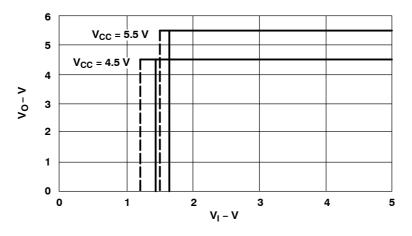

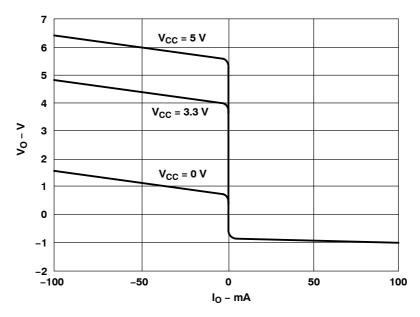

Figures 8 and 9 show the graphs of  $V_O$  versus  $V_I$  for the AHC04 and the AHCT04. The recommended operating range for the AHC family is from 2 V to 5.5 V. For the AHCT the recommended range is from 4.5 V to 5.5 V. Input hysteresis of typically 150 mV is included in AHC devices (300 mV in AHCT devices), which ensures the devices are free from oscillations by increasing the noise margin around the threshold voltage during low-input transitions.

Figure 8. Output Voltage Versus Input Voltage (AHC04)

Figure 9. Output Voltage Versus Input Voltage (AHCT04)

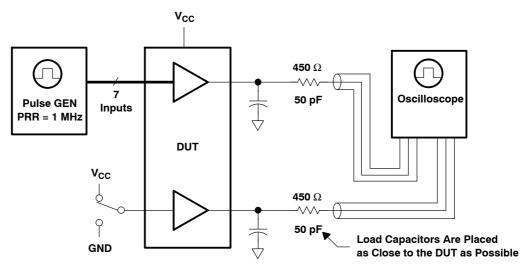

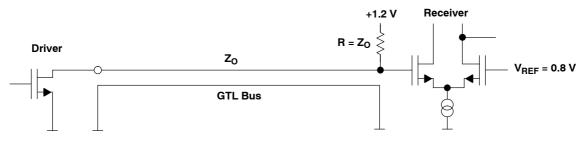

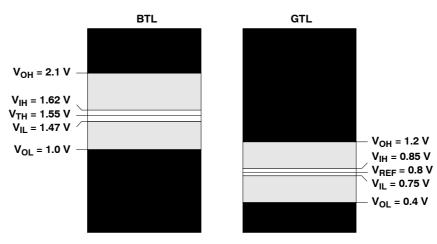

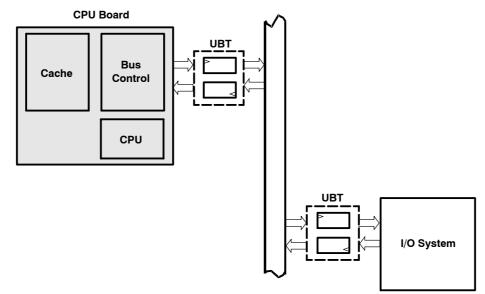

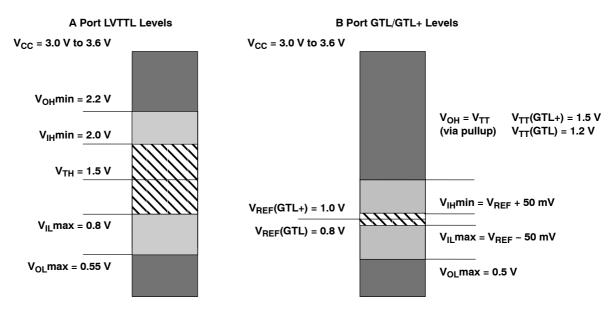

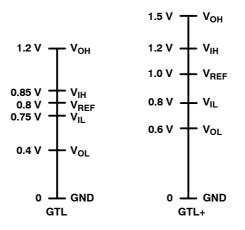

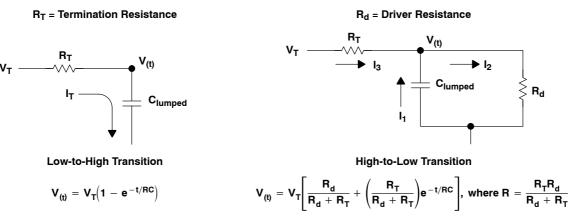

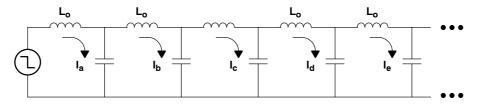

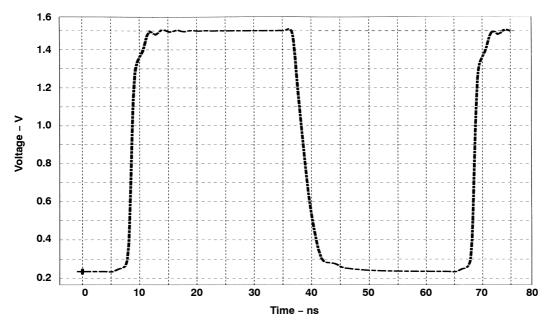

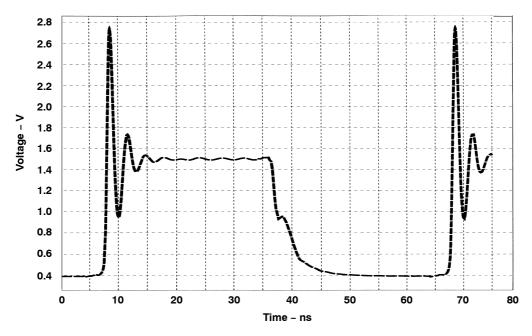

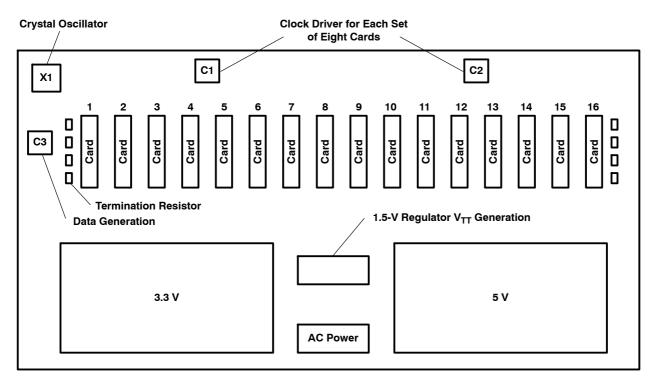

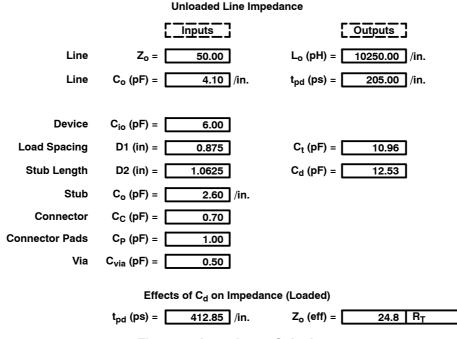

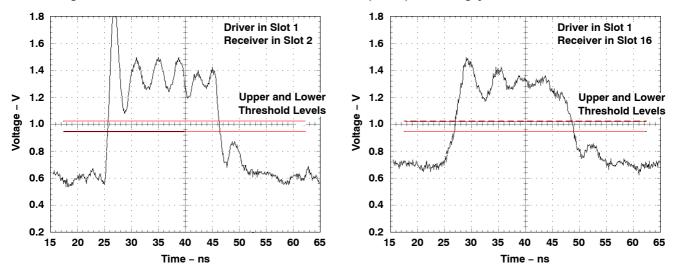

#### Input Current Loading